# CMSC 313 COMPUTER ORGANIZATION & ASSEMBLY LANGUAGE PROGRAMMING

Lecture 21, Fall 2014

## **TOPICS TODAY**

- Circuits for Addition

- Standard Logic Components

- Logisim Demo

# CIRCUITS FOR ADDITION

- Combinational logic circuits give us many useful devices.

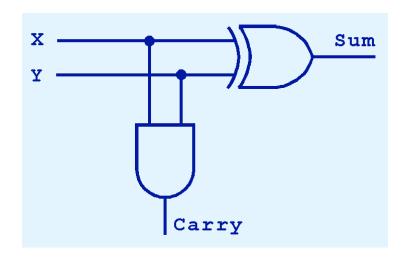

- One of the simplest is the half adder, which finds the sum of two bits.

- We can gain some insight as to the construction of a half adder by looking at its truth table, shown at the right.

| uts | Outputs     |                    |  |  |

|-----|-------------|--------------------|--|--|

| Y   | Sum         | Carry              |  |  |

| 0   | 0           | 0                  |  |  |

| 1   | 1           | 0                  |  |  |

| 0   | 1           | 0                  |  |  |

| 1   | 0           | 1                  |  |  |

|     | 0<br>1<br>0 | Y Sum  0 0 1 1 0 1 |  |  |

#### Half Adder

• Inputs: A and B

• Outputs: S =lower bit of A + B,  $c_{out} =$ carry bit

| A | B | S | $c_{ m out}$ |

|---|---|---|--------------|

| 0 | 0 | 0 | 0            |

| 0 | 1 | 1 | 0            |

| 1 | 0 | 1 | 0            |

| 1 | 1 | 0 | 1            |

- Using Sum-of-Products:  $S = \overline{A}B + A\overline{B}$ ,  $c_{\text{out}} = AB$ .

- Alternatively, we could use XOR:  $S = A \oplus B$ .

As we see, the sum can be found using the XOR operation and the carry using the AND operation.

| Inj | puts | Outputs |       |  |

|-----|------|---------|-------|--|

| X   | Y    | Sum     | Carry |  |

| 0   | 0    | 0       | 0     |  |

| 0   | 1    | 1       | 0     |  |

| 1   | 0    | 1       | 0     |  |

| 1   | 1    | 0       | 1     |  |

|     |      |         |       |  |

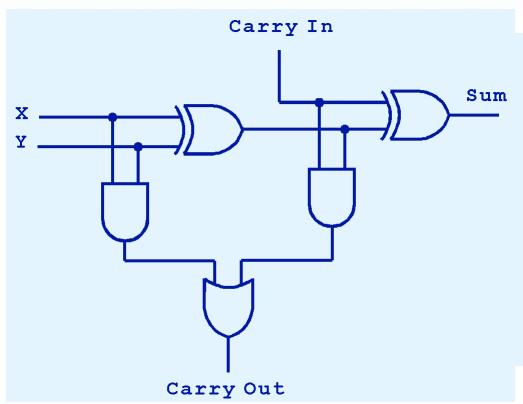

- We can change our half adder into to a full adder by including gates for processing the carry bit.

- The truth table for a full adder is shown at the right.

|   | Inputs |             |   | Outputs          |  |  |

|---|--------|-------------|---|------------------|--|--|

| x | Y      | Carry<br>In |   | Carry<br>Sum Out |  |  |

| 0 | 0      | 0           | 0 | 0                |  |  |

| 0 | 0      | 1           | 1 | 0                |  |  |

| 0 | 1      | 0           | 1 | 0                |  |  |

| 0 | 1      | 1           | 0 | 1                |  |  |

| 1 | 0      | 0           | 1 | 0                |  |  |

| 1 | 0      | 1           | 0 | 1                |  |  |

| 1 | 1      | 0           | 0 | 1                |  |  |

| 1 | 1      | 1           | 1 | 1                |  |  |

#### Full Adder

• Inputs: A, B and  $c_{\rm in}$

• Outputs: S =lower bit of A + B,  $c_{out} =$ carry bit

| A | В | $c_{\rm in}$ | S | $c_{ m out}$ |

|---|---|--------------|---|--------------|

| 0 | 0 | 0            | 0 | 0            |

| 0 | 0 | 1            | 1 | 0            |

| 0 | 1 | 0            | 1 | 0            |

| 0 | 1 | 1            | 0 | 1            |

| 1 | 0 | 0            | 1 | 0            |

| 1 | 0 | 1            | 0 | 1            |

| 1 | 1 | 0            | 0 | 1            |

| 1 | 1 | 1            | 1 | 1            |

- $S = \overline{A}\overline{B}C + \overline{A}B\overline{C} + A\overline{B}\overline{C} + ABC = A \oplus B \oplus C$ .

- $c_{\text{out}} = \text{MAJ3} = AB + BC + AC$ .

Here's our completed full adder.

| Inputs |   |             | Outputs |              |  |

|--------|---|-------------|---------|--------------|--|

| x      | Y | Carry<br>In | Sum     | Carry<br>Out |  |

| 0      | 0 | 0           | 0       | 0            |  |

| 0      | 0 | 1           | 1       | 0            |  |

| 0      | 1 | 0           | 1       | 0            |  |

| 0      | 1 | 1           | 0       | 1            |  |

| 1      | 0 | 0           | 1       | 0            |  |

| 1      | 0 | 1           | 0       | 1            |  |

| 1      | 1 | 0           | 0       | 1            |  |

| 1      | 1 | 1           | 1       | 1            |  |

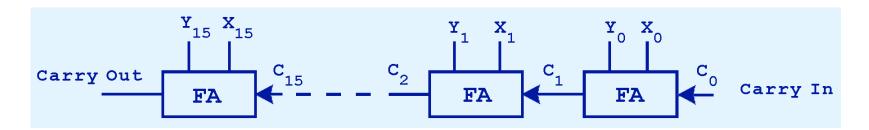

- Just as we combined half adders to make a full adder, full adders can connected in series.

- The carry bit "ripples" from one adder to the next; hence, this configuration is called a *ripple-carry* adder.

Today's systems employ more efficient adders.

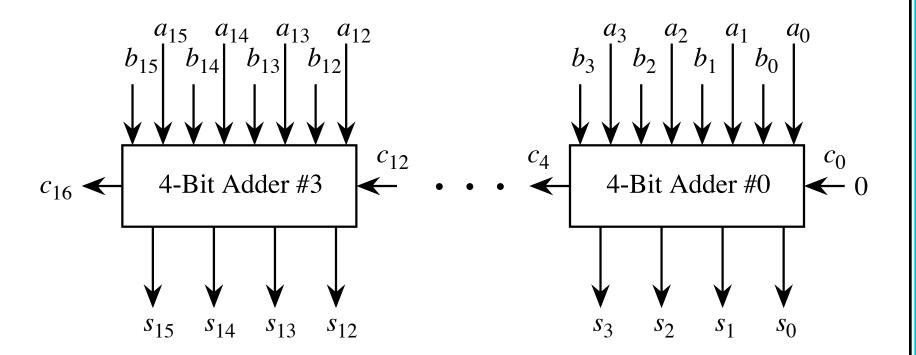

## **Constructing Larger Adders**

• A 16-bit adder can be made up of a cascade of four 4-bit ripple-carry adders.

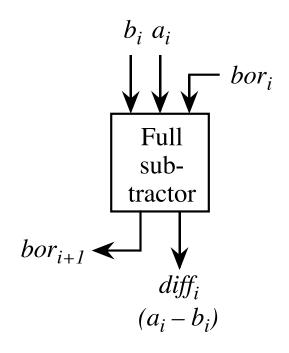

## **Full Subtractor**

Truth table and schematic symbol for a ripple-borrow subtractor:

| $a_i$ | $b_i$ | $bor_i$ | $diff_i$ | $bor_{i+1}$ |

|-------|-------|---------|----------|-------------|

| 0     | 0     | 0       | 0        | 0           |

| 0     | 0     | 1       | 1        | 1           |

| 0     | 1     | 0       | 1        | 1           |

| 0     | 1     | 1       | 0        | 1           |

| 1     | 0     | 0       | 1        | 0           |

| 1     | 0     | 1       | 0        | 0           |

| 1     | 1     | 0       | 0        | 0           |

| 1     | 1     | 1       | 1        | 1           |

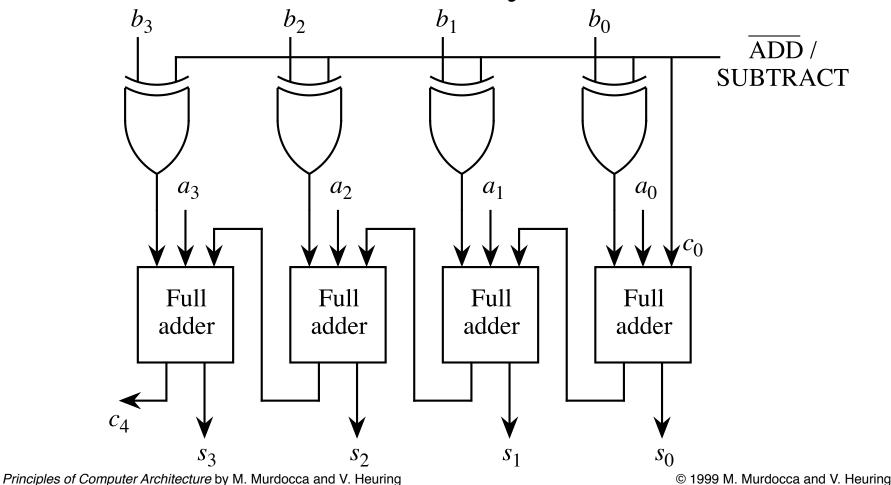

## Combined Adder/Subtractor

• A single ripple-carry adder can perform both addition and subtraction, by forming the two's complement negative for B when subtracting. (Note that +1 is added at  $c_0$  for two's complement.)

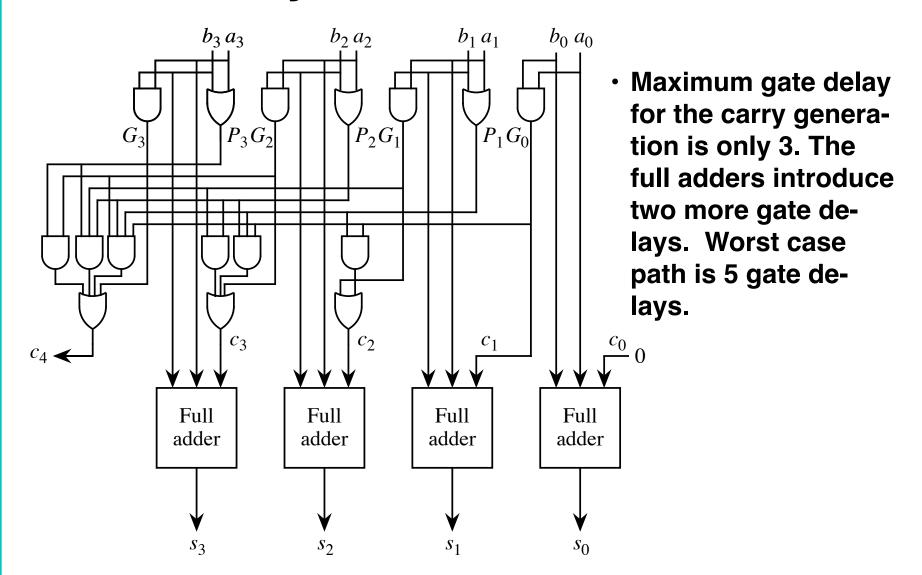

## **Carry-Lookahead Addition**

$$s_{i} = \overline{a_{i}}\overline{b_{i}}c_{i} + \overline{a_{i}}b_{i}\overline{c_{i}} + a_{i}\overline{b_{i}}\overline{c_{i}} + a_{i}b_{i}c_{i}$$

$$c_{i+1} = b_{i}c_{i} + a_{i}c_{i} + a_{i}b_{i}$$

$$c_{i+1} = a_{i}b_{i} + (a_{i} + b_{i})c_{i}$$

$$c_{i+1} = G_{i} + P_{i}c_{i}$$

• Carries are represented in terms of  $G_i$  (generate) and  $P_i$  (propagate) expressions.

$$G_i = a_i b_i$$

and  $P_i = a_i + b_i$

$c_0 = 0$

$c_1 = G_0$

$c_2 = G_1 + P_1 G_0$

$c_3 = G_2 + P_2 G_1 + P_2 P_1 G_0$

$c_4 = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0$

## **Carry Lookahead Adder**

## STANDARD LOGIC COMPONENTS

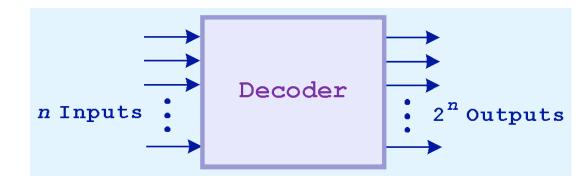

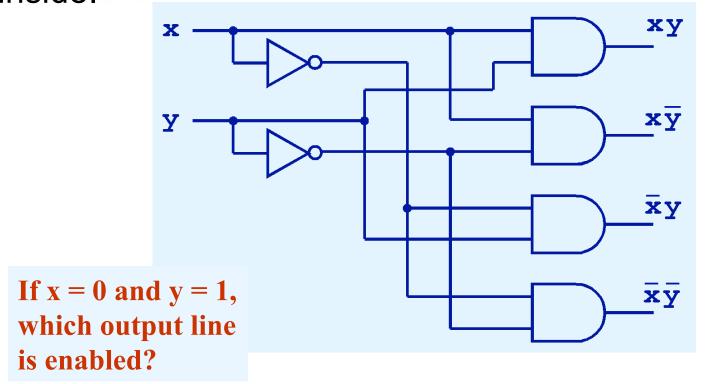

- Decoders are another important type of combinational circuit.

- Among other things, they are useful in selecting a memory location according a binary value placed on the address lines of a memory bus.

Address decoders with n inputs can select any of 2<sup>n</sup>

locations.

This is a block diagram for a decoder.

This is what a 2-to-4 decoder looks like on the inside.

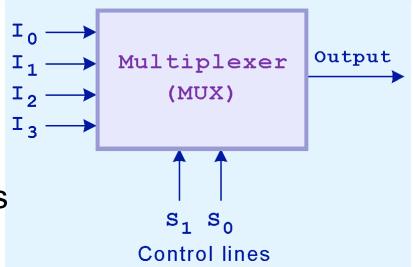

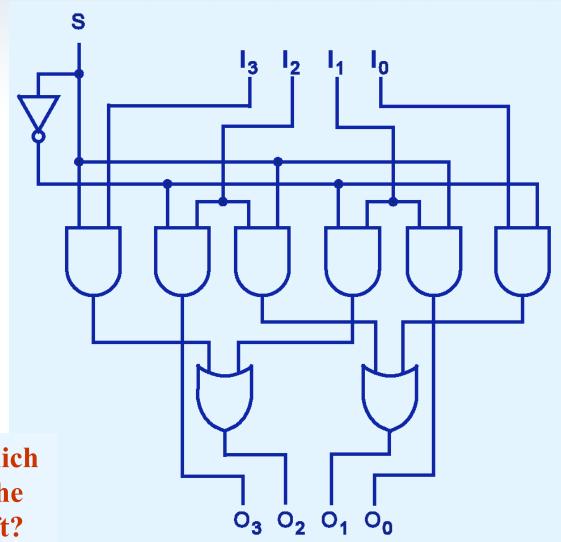

- A multiplexer does just the opposite of a decoder.

- It selects a single output from several inputs.

- The particular input chosen for output is determined by the value of the multiplexer's control lines.

- To be able to select among n inputs, log<sub>2</sub>n control lines are needed.

This is a block diagram for a multiplexer.

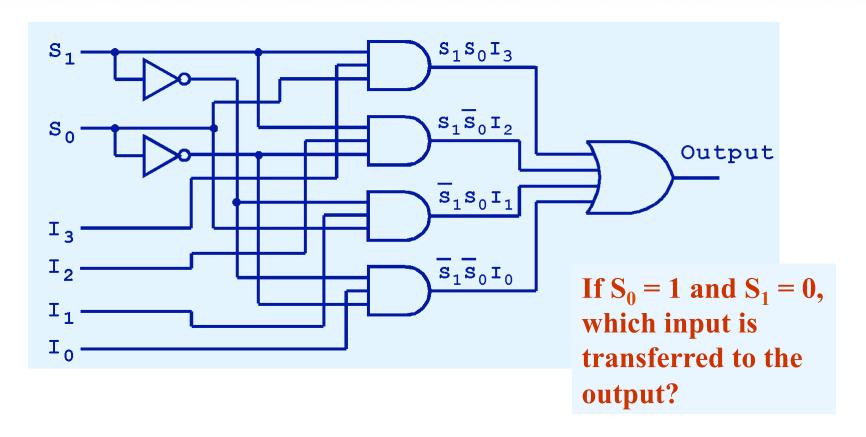

This is what a 4-to-1 multiplexer looks like on the inside.

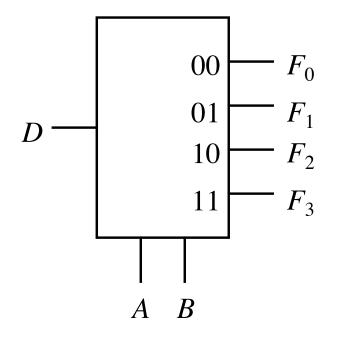

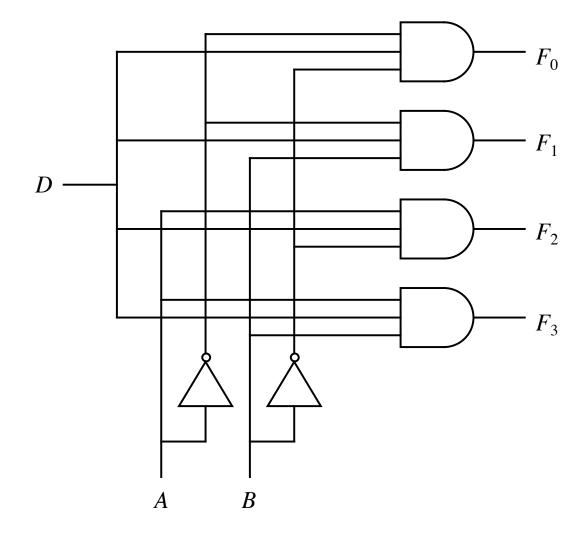

## Demultiplexer

$$F_0 = D\overline{A}\overline{B}$$

$F_2 = DA\overline{B}$

$F_1 = D\overline{A}B$   $F_3 = DAB$

| D | A | В | $F_0$ | $F_1$ | $F_2$ | $F_3$ |

|---|---|---|-------|-------|-------|-------|

| 0 | 0 | 0 | 0     | 0     | 0     | 0     |

| 0 | 0 | 1 | 0     | 0     | 0     | 0     |

| 0 | 1 | 0 | 0     | 0     | 0     | 0     |

| 0 | 1 | 1 | 0     | 0     | 0     | 0     |

| 1 | 0 | 0 | 1     | 0     | 0     | 0     |

| 1 | 0 | 1 | 0     | 1     | 0     | 0     |

| 1 | 1 | 0 | 0     | 0     | 1     | 0     |

| 1 | 1 | 1 | 0     | 0     | 0     | 1     |

## **Gate-Level Implementation of DEMUX**

This shifter moves the bits of a nibble one position to the left or right.

If S = 0, in which direction do the input bits shift?

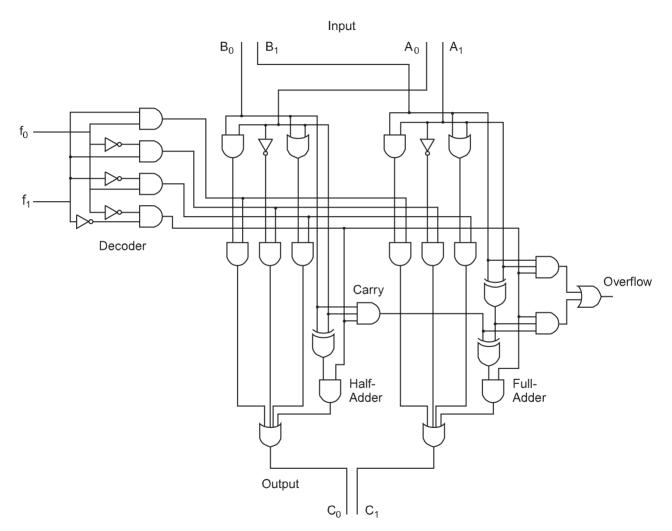

FIGURE 3.17 A Simple Two-Bit ALU

## **NEXT TIME**

- 2-bit ALU

- Flip-flops