#### FAST FOURIER TRANSFORMS ON A DISTRIBUTED DIGITAL SIGNAL PROCESSOR

By

OMAR SATTARI B.S. (University of California, Davis) June, 2002

#### THESIS

Submitted in partial satisfaction of the requirements for the degree of

MASTER OF SCIENCE

in

Electrical and Computer Engineering

in the

#### OFFICE OF GRADUATE STUDIES

of the

#### UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

Chair, Dr. Bevan M. Baas

Member, Dr. Venkatesh Akella

Member, Dr. Hussain Al-Asaad

Committee in charge 2004

© Copyright by Omar Sattari 2004 All Rights Reserved

#### Abstract

Fast Fourier Transforms are used in a variety of Digital Signal Processing applications. As semiconductor process technology becomes more refined, the ability to implement faster and more efficient FFTs increases. However, due to the high costs and design time of custom FFT processors, implementation of the FFT on programmable or reconfigurable platforms is practical. In this work, we present mapping of FFTs of various lengths to a programmable, reconfigurable array of processors. The design of hardware address generators is also presented, as it is tightly coupled with implementation of the Fast Fourier Transform. The reconfigurable array of processors is named Asynchronous Array of Simple Processors (AsAP). A Register Transfer Level (RTL) model of the AsAP architecture is used to simulate Fast Fourier Transforms. Coding for the FFTs is done primarily with assembly-level code. Three FFTs of length 32, 64, and 1024 points were mapped and simulated onto AsAP. The accuracy of each FFT was verified by comparing simulation results to an independent model.

#### Acknowledgments

I would like to thank my advisor, Professor Bevan Baas. In addition to guiding me through this research, he has taught me lessons which I know have made me a better engineer. His willingness to spend time with me is sincerely appreciated.

I thank Professor Venkatesh Akella and Professor Hussain Al-Asaad for their valuable insight and their consultation. Their different perspectives helped me produce a better thesis.

The University of California, Davis has provided a stable, enriching environment for me to study in, and I am grateful for that. I would like to thank Alza Corporation for providing me with a scholarship that has helped me make this journey. Intel corporation has donated computing equipment which accelerated research in the VCL lab; thank you.

To Mike Lai, Mike Meeuwsen, Ryan Apperson, and Zhiyi Yu, I have thoroughly enjoyed the time we spent together in the VCL lab. Interaction with you has helped advance my research. Thank you for the discussions, the debates, the comedy, and the respect.

My father Saied and my mother Najla have made education the top priority throughout my life. They have provided a warm and loving home, in addition to supporting my education and my interests. There is no way I can reciprocate the twenty four years of sacrifice you have made for me and my siblings. I can only thank you.

To my sister Nazaneen, and my brother Haroon, thanks for encouraging me and showing me how much you love me. I am faithfully waiting for the days that I can celebrate your great accomplishments with you.

## Contents

| A             | bstra                     | let                               | iii                |

|---------------|---------------------------|-----------------------------------|--------------------|

| A             | cknov                     | wledgments                        | iv                 |

| $\mathbf{Li}$ | st of                     | Figures                           | vii                |

| $\mathbf{Li}$ | st of                     | Tables                            | viii               |

| 1             | <b>Intr</b><br>1.1<br>1.2 | oduction<br>Project Goals         | <b>1</b><br>1<br>1 |

| <b>2</b>      | Dise                      | crete and Fast Fourier Transforms | 3                  |

|               | 2.1                       | The Continuous Fourier Transform  | 3                  |

|               | 2.2                       | The Discrete Fourier Transform    | 4                  |

|               | 2.3                       | The Fast Fourier Transform        | 5                  |

| 3             | FFI                       | <b>F</b> Implementation           | 7                  |

|               | 3.1                       | Butterflies                       | 8                  |

|               | 3.2                       | Memory Requirements               | 8                  |

|               | 3.3                       | Memory Access Patterns            | 9                  |

|               | 3.4                       | Bit Reversal                      | 11                 |

|               | 3.5                       | Related Work                      | 12                 |

| <b>4</b>      | The                       | AsAP DSP                          | <b>14</b>          |

|               | 4.1                       | Array Topology                    | 16                 |

|               | 4.2                       | Instruction Set                   | 17                 |

|               | 4.3                       | Memories                          | 17                 |

|               | 4.4                       | FIFOs                             | 19                 |

|               | 4.5                       | Datapath and Pipeline             | 19                 |

|               | 4.6                       | Configuration                     | 20                 |

|               | 4.7                       | Local Clock Generators            | 21                 |

| 5             | Add                       | dress Generation Hardware         | 23                 |

| -             | 5.1                       | Address Generator Interface       | $\frac{-3}{23}$    |

|               | 5.2                       | Address Generator Design          | 25                 |

| 6  | Map   | oping H | FFTs on to AsAP                                                                                                                                                                                                                                        |   |     |   |       |   |   | <b>28</b> |

|----|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|-------|---|---|-----------|

|    | 6.1   | Using 1 | Address Pointers and Address Generators                                                                                                                                                                                                                |   |     |   |       |   |   | . 28      |

|    |       | 6.1.1   | Address Pointers                                                                                                                                                                                                                                       |   |     |   |       |   |   | . 29      |

|    |       | 6.1.2   | Address Generators                                                                                                                                                                                                                                     |   |     |   |       |   |   | . 30      |

|    | 6.2   | Butter  | flies                                                                                                                                                                                                                                                  |   |     |   |       |   |   | . 31      |

|    | 6.3   | Bit-Re  | versal                                                                                                                                                                                                                                                 |   |     |   |       |   |   | . 36      |

|    | 6.4   | Memor   | y Addressing                                                                                                                                                                                                                                           |   |     |   |       |   |   | . 36      |

|    | 6.5   | Long F  | FTs                                                                                                                                                                                                                                                    |   |     |   |       | • |   | . 38      |

|    |       | 6.5.1   | The Cached FFT Algorithm                                                                                                                                                                                                                               | • | • • |   | <br>• |   | • | . 39      |

|    |       | 6.5.2   | Large Memories                                                                                                                                                                                                                                         | • | ••• | • | <br>• | • | • | . 41      |

| 7  | FFJ   | ls impl | emented on AsAP                                                                                                                                                                                                                                        |   |     |   |       |   |   | 43        |

|    | 7.1   | _       | nt FFT                                                                                                                                                                                                                                                 |   |     |   |       |   |   |           |

|    |       | 7.1.1   | Bit Reverse Processor                                                                                                                                                                                                                                  |   |     |   |       |   |   |           |

|    |       | 7.1.2   | Butterfly Processor                                                                                                                                                                                                                                    |   |     |   |       |   |   | . 45      |

|    | 7.2   | 64-Poir | $\operatorname{nt}\operatorname{FFT}\stackrel{\circ}{\overset{\circ}{\ldots}}\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ |   |     |   |       |   |   |           |

|    |       | 7.2.1   | Memory Processor                                                                                                                                                                                                                                       |   |     |   |       |   |   | . 50      |

|    |       | 7.2.2   | Butterfly Processor                                                                                                                                                                                                                                    |   |     |   |       |   |   | . 52      |

|    |       | 7.2.3   | Shuffle Processor                                                                                                                                                                                                                                      |   |     |   |       |   |   | . 54      |

|    |       | 7.2.4   | Eight Processor Version                                                                                                                                                                                                                                |   |     |   |       |   |   | . 55      |

|    | 7.3   | 1024-P  | oint FFT                                                                                                                                                                                                                                               |   |     |   |       |   |   | . 56      |

|    |       | 7.3.1   | Bit Reverse Processor $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                      | • |     |   |       |   | • | . 57      |

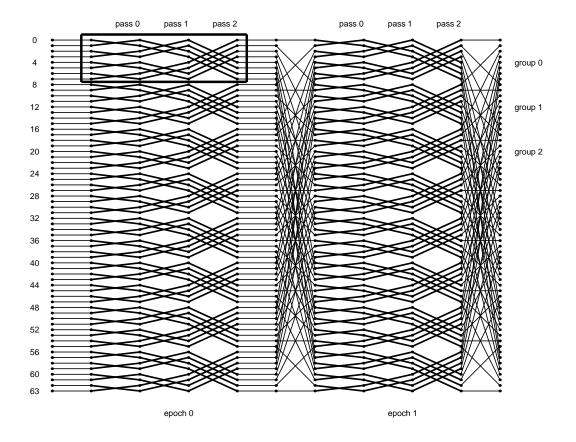

|    |       | 7.3.2   | First-Epoch Shuffle Processor                                                                                                                                                                                                                          |   |     |   |       |   | • | . 61      |

|    |       | 7.3.3   | Second-Epoch Twiddle Factor Generator Processor                                                                                                                                                                                                        | • |     | • | <br>• | • | • | . 63      |

| 8  | Con   | clusion | 1                                                                                                                                                                                                                                                      |   |     |   |       |   |   | 69        |

|    | 8.1   | Contril | butions                                                                                                                                                                                                                                                |   |     |   |       |   |   | . 69      |

|    | 8.2   | Future  | Work                                                                                                                                                                                                                                                   |   |     |   |       |   |   | . 69      |

|    |       | 8.2.1   | Assembly Code for a Pipelined AsAP Architecture                                                                                                                                                                                                        |   |     |   |       |   |   | . 69      |

|    |       | 8.2.2   | Performance Optimizations                                                                                                                                                                                                                              |   |     |   | <br>• |   |   | . 70      |

| Bi | bliog | raphy   |                                                                                                                                                                                                                                                        |   |     |   |       |   |   | 71        |

# List of Figures

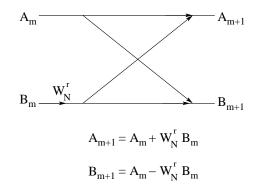

| 2.1 | A radix-2 FFT butterfly 5                                    |

|-----|--------------------------------------------------------------|

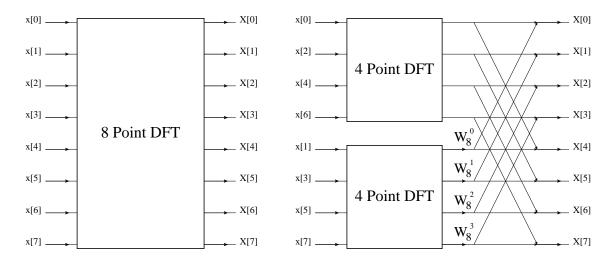

| 2.2 | An 8-point DFT decomposed to two 4-point DFTs 5              |

| 2.3 | An 8-point FFT                                               |

| 3.1 | Bit Reversed Addresses 11                                    |

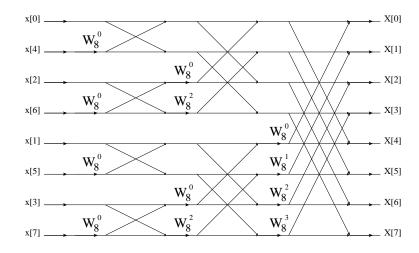

| 4.1 | A block diagram for a single AsAP processor                  |

| 4.2 | Dataflow for a fine-granularity 8-tap FIR filter 16          |

| 4.3 | Sample configuration code for an application                 |

| 4.4 | Sample assembly code to load constants for an application    |

| 4.5 | Sample assembly code for an application                      |

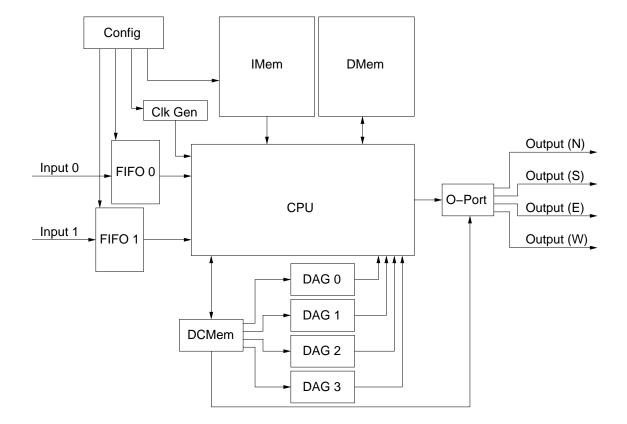

| 4.6 | An overview of configuration and testing                     |

| 5.1 | Data Address Generator    25                                 |

| 5.2 | Example of Split-Mask-Lo Operation                           |

| 6.1 | Dynamic Configuration Memory Map                             |

| 6.2 | A 16-bit multiplication                                      |

| 6.3 | A special fixed-point multiply                               |

| 6.4 | FFT Butterfly Error                                          |

| 6.5 | A 64-point Cached-FFT dataflow diagram                       |

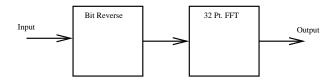

| 7.1 | Dataflow diagram for a two-processor 32-point complex FFT    |

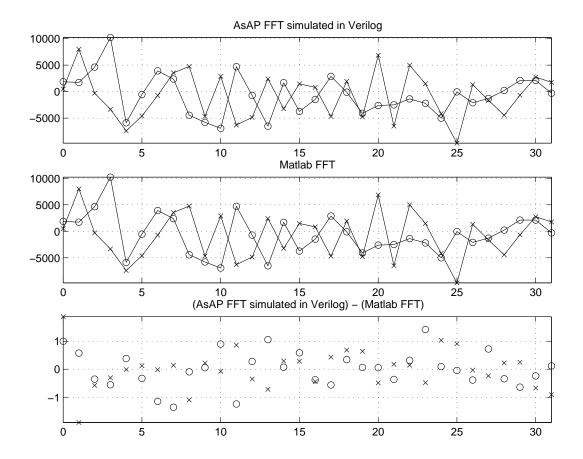

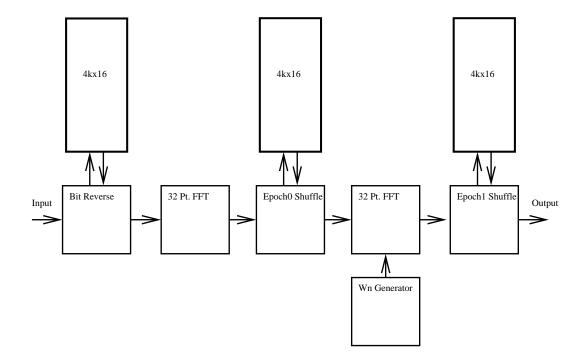

| 7.2 | 32-Point FFT Accuracy 49                                     |

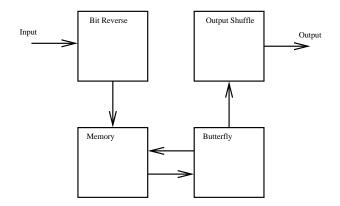

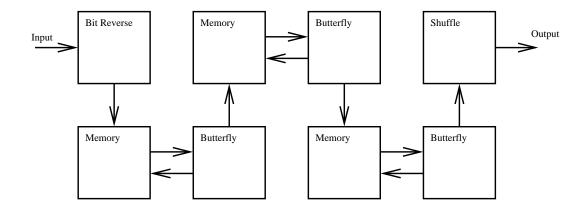

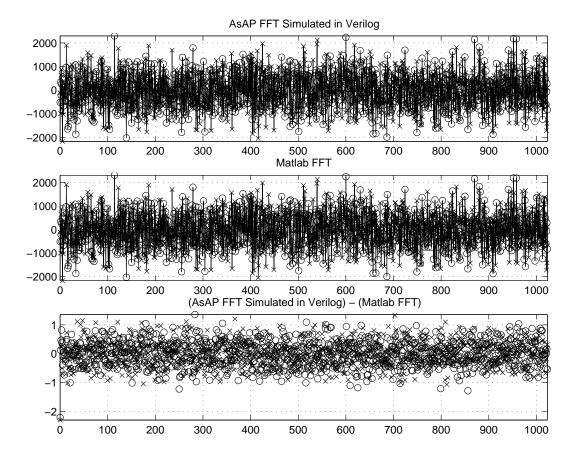

| 7.3 | Dataflow diagram for a 4-processor 64-point complex FFT      |

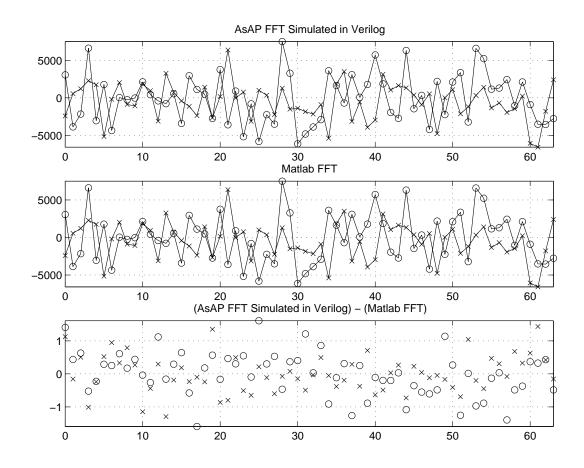

| 7.4 | 64-Point FFT Accuracy 55                                     |

| 7.5 | Dataflow diagram for an eight-processor 64-point complex FFT |

| 7.6 | Dataflow diagram for a 6-processor 1024-point complex FFT 57 |

| 7.7 | 1024-Point FFT Accuracy                                      |

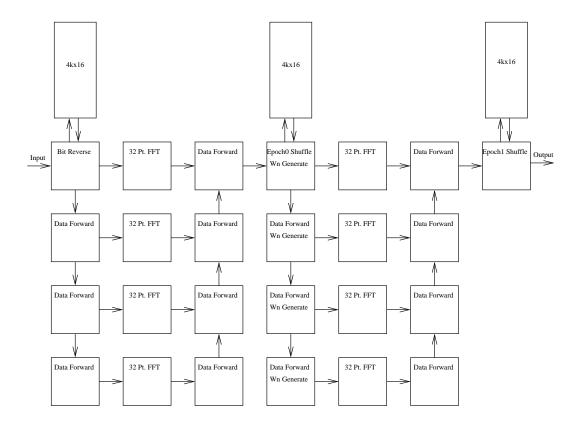

| 7.8 | Dataflow diagram for a 25-processor 1024-point complex FFT   |

# List of Tables

| 8-Point FFT data addresses                                                    | 10                            |

|-------------------------------------------------------------------------------|-------------------------------|

| 8-Point FFT twiddle addresses                                                 | 10                            |

| Addresses for a 64-point FFT                                                  | 10                            |

| Real and Imaginary addresses for a 64-point FFT                               | 11                            |

| FFTs Implemented on Processors                                                | 13                            |

| Instruction Formats                                                           | 18                            |

| Address Generator Inputs                                                      | 24                            |

| Real and Imaginary addresses for a 64-point Cached FFT $\ldots \ldots \ldots$ | 41                            |

| Real and Imaginary addresses for a two-epoch 1024-point Cached FFT            | 58                            |

| Real and Imaginary addresses for memory shuffle in a 1024-point Cached FFT    | 58                            |

| Processor Utilization for FFT Applications                                    | 67                            |

|                                                                               | 8-Point FFT twiddle addresses |

### Chapter 1

### Introduction

The Fast Fourier Transform (FFT) is an essential algorithm in digital signal processing. It is employed in various applications such as radar, wireless communication, medical imaging, spectral analysis, and acoustics. Fast Fourier Transforms have been implemented on different platforms, ranging from general purpose processors to specially designed computer chips. Recent increases in microchip fabrication costs have made it more difficult to produce custom designs for applications. Implementation of digital signal processing algorithms, such as the FFT, on high-performance reconfigurable systems is becoming increasingly attractive.

#### 1.1 Project Goals

The goal of this project is to implement Fast Fourier Transforms on a parallel, reconfigurable processor array. Also, compromises between processor area and computational throughput will be explored.

#### 1.2 Overview

Chapter 2 introduces the Discrete Fourier Transform and the radix-2 Decimation in Time Fast Fourier Transform. In Chapter 3, FFT implementation techniques are discussed, as well as related work on the topic of FFT implementation. Chapter 4 presents the AsAP architecture, which FFTs will be mapped onto. Chapter 5 introduces the address generators that were designed for AsAP as part of this work. Chapter 6 is a discussion on how to map algorithms specifically to the AsAP DSP, and includes an introduction to the Cached FFT Algorithm. Chapter 7 presents each of the FFTs implemented on AsAP, including assembly source code.

### Chapter 2

# Discrete and Fast Fourier Transforms

This chapter presents the Continuous Fourier transform, the Discrete Fourier Transform, and the Fast Fourier Transform. This presentation, which assumes background knowledge in signal processing, is brief. For a more in-depth analysis and history of these topics, several introductory textbooks [1, 2] can be consulted.

#### 2.1 The Continuous Fourier Transform

The Continuous Fourier Transform describes the transformation of a function from one domain of representation to another. The Fourier Transform is defined by Eq. 2.1. In signal processing, the two domains are usually time and frequency, so that x is replaced with t, and s is replaced with  $\omega$ .

$$F(s) = \int_{-\infty}^{\infty} f(x)e^{-i2\pi xs}dx$$

(2.1)

Equation 2.1 is known as the *Forward Fourier Transform*. The *Inverse Fourier Transform* also exists, and is defined by Eq. 2.2.

$$f(x) = \int_{-\infty}^{\infty} F(s)e^{i2\pi xs}ds$$

(2.2)

Not all functions are guaranteed to have Fourier Transforms. A common test to determine if a Fourier Transform exists for a function is the "Dirichlet Conditions" [2]. The two Dirichlet Conditions for the existence of a Fourier Transform are that the function has a finite integral over its entire domain, and that the function is continuous or has only finite discontinuities. Although these conditions guarantee the existence of the Fourier Transform for a function, there are functions that do not meet the conditions but still have Fourier Transforms. For this reason, the Dirichlet Conditions are sufficient but not necessary conditions to prove the existence of a Fourier Transform.

#### 2.2 The Discrete Fourier Transform

The Discrete Fourier Transform converts discrete data from one domain to another. The data (a series of points) must have finite length, and usually represents the periodic sampling of a continuous signal. Equation 2.3 describes X(k), the DFT of an N-point input sequence x(n). X(k), which also is of length N, is the frequency domain representation of x(n).

$$X(k) = \sum_{n=0}^{N-1} x(n) e^{-i2\pi nk/N}, \quad k = 0, 1, ..., N-1$$

(2.3)

A different (shorter) way to define the DFT is Eq. 2.4.

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nk}, \quad k = 0, 1, ..., N-1$$

(2.4)

In this context,  $W_N$  is known as the twiddle factor and is defined by,

$$W_N = e^{-i2\pi/N}$$

(2.5)

Using the twiddle factor, the definition of the inverse DFT is,

$$x(n) = \frac{1}{N} \sum_{n=0}^{N-1} X(k) W_N^{-nk}, \quad n = 0, 1, ..., N-1 .$$

(2.6)

The DFT is better-suited for implementation on computers than the continuous Fourier Transform. Computers can store only a finite set of data in memory, and have no way to fully represent a continuous signal using individual points. DFTs are transforms of finitelength sequences, which can be represented in computers (notwithstanding quantization error of individual points). Implementing the DFT or inverse DFT on a computer will require 2N memory locations in addition to the memory space required to (if necessary)

Figure 2.1: A radix-2 FFT butterfly

Figure 2.2: An 8-point DFT decomposed to two 4-point DFTs

store all of the twiddle factors as constants. A sum of 2N memory locations are required because N memory locations are occupied by x(n), and the other N are occupied by the result, X(k). Approximately  $N^2$  complex multiplications and N(N-1) complex additions are required to complete a DFT or inverse DFT of an input sequence of length N.

#### 2.3 The Fast Fourier Transform

Fast Fourier Transform is a group of algorithms that are more computationally efficient than the standard DFT. Cooley and Tukey are noted most often for presenting the algorithm in a research paper [3] for the journal "Mathematics of Computation." We discuss

Figure 2.3: An 8-point FFT

the key points of FFTs instead of presenting a derivation of the entire class of algorithms. There are textbooks that present the derivation, along with a thorough discussion of FFT algorithms [1, 2]. The FFTs discussed in this work are Decimation-In-Time (DIT), radix-2 FFTs. Decimation-In-Time FFTs focus on reorganizing the input sequence x[n] to reduce computation. The length of the input sequence is always a power of two in radix-2 FFTs.

The DIT FFT is more efficient than the DFT because the FFT is a recursive decomposition of the DFT into smaller and smaller DFTs. The smallest useful DFT is a radix-2 butterfly. Figure 2.1 describes a radix-2 butterfly. An FFT of length N can be reduced to two separate FFTs of length N/2, followed by N/2 butterflies. Figure 2.2 is a data flow diagram that shows how an 8-point DFT can be reduced in such a manner. The decomposition can be continued until only radix-2 butterflies remain, as in Fig. 2.3. This figure shows that there are 4 butterflies per stage in an 8-point FFT. Each butterfly requires a complex multiplication and two complex additions (one add, one subtract). There are  $\log_2(N)$  stages for an N-point FFT. Therefore, there are  $N/2 \log_2(N)$  complex multiplies per FFT, and  $N \log_2(N)$  complex additions per FFT. A standard DFT requires  $N^2$  operations because for each output point in X[k] the entire input sequence x[n] is multiplied by a twiddle factor. For long FFTs,  $N \log_2(N)$  operations are orders of magnitude fewer than  $N^2$ .

### Chapter 3

### **FFT** Implementation

Implementation of DIT FFTs on digital computers can be done in various ways depending on the computer hardware available. Memory space and processor capabilities are two factors to consider for implementation. Processors that have floating point hardware can provide very accurate results, but are complex. Processors that don't have floating point hardware are usually limited to simpler implementations of the FFT, such as fixed-point or block floating point. We focus on fixed-point implementations of the FFT, which have more error than floating-point, but use only integer arithmetic.

First, we will briefly investigate the memory access patterns in the FFT, to give insight on how to map the algorithm. Figure 2.3 shows that the indices of the output X[k]are in consecutive order, but the input x[k] is not, and has a complicated pattern. With a similar dataflow, it is possible to switch the order of input and output, so that the input is consecutive and the output is irregular. In order to have both the input and output in consecutive order, the dataflow needs to be changed significantly, and the pattern of data access becomes extremely complicated. Instead of changing the dataflow inside of the FFT, it's easier to simply presort the input data to match the complex pattern, before computation of the FFT.

#### 3.1 Butterflies

Each point in x[k] has a real component and an imaginary component. As a result, a complex multiplication requires four integer multiplies and two integer additions. The following equation is an example of an expanded complex multiplication, where  $j = \sqrt{-1}$ .

$$(a+bj)(c+dj) = (ac-bd) + j(ad+bc)$$

(3.1)

For a butterfly, there are two complex additions one complex multiplication. This brings the total number of integer computations to four multiplies and four adds.

#### **3.2** Memory Requirements

Since the FFT breaks the Fourier Transform (conveniently) into stages, it is necessary to have only one array that can hold all N points. Once a stage is complete, the only consumer of its data is the next stage, so the same array of points can be used over and over as a conduit between stages. Still, when implementing the FFT on a computer, it is advantageous to have more memory than the number of inputs N. If there is enough memory to accommodate all N inputs and all N/2 twiddle factors, most FFT algorithms allow all butterflies to be executed "in-place." This means that for each butterfly, the inputs are loaded from the appropriate locations, the butterfly is computed, and the results are stored back to the original locations. As a result of using this method, all the butterflies in a single stage should be executed and their results stored before moving on to the next stage. However, in a single stage, the butterflies need not be executed in any particular order, because no two butterflies share the same input or output.

Each point in an FFT has a real component and an imaginary component. Considering the example of a 16-bit complex point, the point can be stored as a single 32-bit word, or as two separate 16-bit words. We consider the case where a point is stored as two memory words. For an 8-point FFT, 16 words of memory are therefore necessary. Also, there are four unique twiddle factors, so an additional eight words of memory are required, unless the twiddle factors are supplied by an outside source. It is also possible to compute twiddle factors as they become necessary, however this may reduce the effective throughput of the FFT if there is only one computation engine and FFTs are being executed repeatedly. There is a trade-off here, between memory space and computation time. We assume that all twiddle factors are stored in memory. In this case, an N-point FFT requires 2N memory words to store data, and N words to store twiddle factors, for a total of 3N memory words.

#### 3.3 Memory Access Patterns

The pattern of memory reads (and writes) that an in-place DIT FFT exhibits is fairly complex. Table 3.1 shows the memory accesses for data points in an 8-point FFT. Each butterfly accesses four locations, since imaginary and real components are separate memory words. Table 3.2 shows memory accesses for the twiddle factors in an 8-point FFT. As the length of the FFT grows, the memory accesses in the FFT follow a predictable (albeit complicated) pattern. In an N-point FFT, there are  $\log_2 N$  stages. In any particular stage, the addresses for each butterfly can be generated using a simple binary counter with a modification. The modification is that in different stages, a single bit is "injected" between bits in the binary count. There are N points per stage of butterflies, so the binary counter needs  $\log_2(N)$  bits. However, since a bit is injected into each address, the counter need be only  $\log_2(N) - 1$  bits wide. The value of the injected bit differentiates between the addresses for a 64-point FFT. The injected bit is labeled I, and the counter bits are  $c_4, c_3, c_2, c_1$ , and  $c_0$ . All addresses presented are with reference to a base address of 0. The address patterns for longer FFTs are straightforward extensions of this table.

The addresses in Table 3.3 assume single entries in memory for each complex point. In our case one bit, which we will name the J bit, is appended to all addresses. It becomes the new least significant bit. This bit will distinguish between the real and imaginary parts of each point. Table 3.4 shows the 64 point FFT address patterns, including the J bit.

|                                 | Stage 0   | Stage 1   | Stage 2   |

|---------------------------------|-----------|-----------|-----------|

| Butterfly 0 addresses (point A) | 0,1       | 0,1       | 0,1       |

| Butterfly 0 addresses (point B) | 2,3       | 4,5       | $^{8,9}$  |

| Butterfly 1 addresses (point A) | 4,5       | 2,3       | 2,3       |

| Butterfly 1 addresses (point B) | 6,7       | 6,7       | $10,\!11$ |

| Butterfly 2 addresses (point A) | 8,9       | 8,9       | 4,5       |

| Butterfly 2 addresses (point B) | 10,11     | $12,\!13$ | $12,\!13$ |

| Butterfly 3 addresses (point A) | 12,13     | 10,11     | 6,7       |

| Butterfly 3 addresses (point B) | $14,\!15$ | $14,\!15$ | $14,\!15$ |

Table 3.1: 8-Point FFT data addresses. The addresses for real and imaginary components of each point are separated by commas.

|                               | Stage 0 | Stage 1 | Stage 2 |

|-------------------------------|---------|---------|---------|

| Butterfly 0 twiddle addresses | 0,1     | 0,1     | 0,1     |

| Butterfly 1 twiddle addresses | 0,1     | 4,5     | 2,3     |

| Butterfly 2 twiddle addresses | 0,1     | 0,1     | 4,5     |

| Butterfly 3 twiddle addresses | 0,1     | 4,5     | 6,7     |

Table 3.2: 8-Point FFT twiddle addresses. The addresses for real and imaginary components of each  $W_N^k$  twiddle factor are separated by commas.

| Stage     | Butterfly Address Bits  | $W_N$ Address Bits         |

|-----------|-------------------------|----------------------------|

| stage 0   | $c_4c_3c_2c_1c_0I$      | $W_{64}^{00000}$           |

| stage $1$ | $c_4c_3c_2c_1Ic_0$      | $W^{c_00000}_{64}$         |

| stage $2$ | $c_4c_3c_2Ic_1c_0$      | $W_{64}^{c_1c_0000}$       |

| stage $3$ | $c_4c_3Ic_2c_1c_0$      | $W_{64}^{c_2c_1c_000}$     |

| stage $4$ | $c_4 I c_3 c_2 c_1 c_0$ | $W_{64}^{c_3c_2c_1c_00}$   |

| stage $5$ | $Ic_4c_3c_2c_1c_0$      | $W_{64}^{c_4c_3c_2c_1c_0}$ |

Table 3.3: Addresses for a 64-point FFT [4]

| Stage     | Butterfly Address Bits    | $W_N$ Address Bits          |

|-----------|---------------------------|-----------------------------|

| stage 0   | $c_4c_3c_2c_1c_0IJ$       | $W_{64}^{00000J}$           |

| stage $1$ | $c_4c_3c_2c_1Ic_0J$       | $W_{64}^{c_00000J}$         |

| stage $2$ | $c_4c_3c_2Ic_1c_0J$       | $W_{64}^{c_1 c_0 000 J}$    |

| stage $3$ | $c_4c_3Ic_2c_1c_0J$       | $W_{64}^{c_2c_1c_000J}$     |

| stage $4$ | $c_4 I c_3 c_2 c_1 c_0 J$ | $W_{64}^{c_3c_2c_1c_00J}$   |

| stage $5$ | $Ic_4c_3c_2c_1c_0J$       | $W_{64}^{c_4c_3c_2c_1c_0J}$ |

Table 3.4: Real and Imaginary addresses for a 64-point FFT [4]

| 0 = 000 | reversed -> | 000 | = | 0 |

|---------|-------------|-----|---|---|

| 1 = 001 | reversed -> | 100 | = | 4 |

| 2 = 010 | reversed -> | 010 | = | 2 |

| 3 = 011 | reversed -> | 110 | = | 6 |

| 4 = 100 | reversed -> | 001 | = | 1 |

| 5 = 101 | reversed -> | 101 | = | 5 |

| 6 = 110 | reversed -> | 011 | = | 3 |

| 7 = 111 | reversed -> | 111 | = | 7 |

Figure 3.1: Bit Reversed Addresses

#### **Bit Reversal 3.4**

If the addresses for the input x[k] are represented in binary format, reversing the order of the bits for a consecutive vector yields exactly the pattern needed for the input vector. This transformation is shown in Fig. 2.3. If x[k] is stored in memory with such an address mapping, both input and output can have consecutive addresses. Implementing the bit-reversal of an address bus is simple when designing hardware; the wires are simply flipped. However, in software this is a complex task. Processors that can reverse the bits of an address (or datum) in hardware provide a very useful feature for FFT implementation.

#### 3.5 Related Work

Recent implementations of the FFT vary in terms of how much hardware and software are used. At one end of the spectrum are chips designed to compute the FFT exclusively. Examples of Application Specific Integrated Circuits (ASICs) for FFT are the 1024-point FFT processors designed and fabricated by He and Torkelson [5] or Baas [6]. In such designs, the application (FFT) is known before design, and the circuit is perfectly matched to the workload.

Parallel architectures for computing the FFT have also been investigated. Shin, Lee, and Lee have designed two-dimensional processor arrays for FFT computation [7, 8]. Yongjun Peng has designed an 8-processor parallel architecture for the computation of 256 through 4096-point FFTs [9]. Each of the processors computes an 8-point FFT using a radix-8 butterfly, and a 1024-point FFT is expected to complete in 3.2  $\mu$ sec.

Another paradigm for FFT implementation is an array of processors designed for multimedia applications, not exclusively FFT. Such implementations usually involve large amounts of software programming, but are very flexible in terms of applications that can be programmed. Examples of such architectures are the MorphoSys Reconfigurable Computation Platform [10], the Imagine Stream Processor [11], and VIRAM [12]. The computation engine in the MorphoSys platform is an array of reconfigurable processing cells. These cells communicate with each other using a data movement unit labeled "Frame Buffer". Various length FFTs were implemented on MorphoSys using radix-2 butterflies. The Imagine processor is a single chip with 48 parallel Arithmetic Logic Units (ALUs). A 1024-point FFT was mapped to Imagine; the 10 stages of butterflies were separated into 10 kernels, and data are transferred between kernels. VIRAM has four 64-bit vector processors, each with its own floating-point unit, in addition to 16 MB of DRAM. FFTs of length 128, 256, 512 and 1024 points were implemented on VIRAM [13].

Although AsAP is also an array of processors, it is designed with DSP applications in mind, and has inherent properties that distinguish it from the mentioned designs. The features of AsAP are discussed in the next chapter. Table 3.5 summarizes the capabilities of various processors on which a 1024-point FFT has been implemented.

| Processor    | Type               | Year | Technology        | Data      | Data Point  | 1024-point FFT        |

|--------------|--------------------|------|-------------------|-----------|-------------|-----------------------|

|              |                    |      |                   | Width     | Format      | Execution Time        |

| TM-66        | Custom FFT         | -    | $0.8 \mu { m m}$  | 32 bit    | float       | $65\mu sec$           |

| Spiffee1     | Custom FFT         | 1995 | $0.7 \mu { m m}$  | 20 bit    | fixed       | $30\mu sec$           |

| DSP-24       | Custom FFT         | 1997 | $0.5 \mu { m m}$  | 24 bit    | block float | $21\mu sec$           |

| Double BW    | Custom FFT         | 2000 | $0.35 \mu { m m}$ | 24 bit    | float       | $10\mu sec$           |

| ADSP 21061   | Programmable DSP   | -    | -                 | -         | float       | $460\mu sec$          |

| VIRAM        | Programmable       | 1999 | -                 | 16-64 bit | float       | $37\mu sec^*$         |

| Imagine      | Programmable       | 2002 | $0.15 \mu { m m}$ | -         | -           | $20.6 \mu sec$        |

| Kuo, Wen, Wu | Programmable FFT   | 2003 | $0.35 \mu { m m}$ | 16  bit   | fixed       | $167 \mu sec$         |

| Peng         | Programmable FFT   | 2003 | $0.18 \mu { m m}$ | 20 bit    | -           | $3.2\mu \text{sec}^*$ |

| AsAP         | Prog., Reconf. DSP | 2004 | $0.13 \mu { m m}$ | 16  bit   | fixed       | $101\mu sec^*$        |

| AsAP         | Prog., Reconf. DSP | 2004 | $0.13 \mu { m m}$ | 16  bit   | fixed       | $30\mu sec^{**}$      |

Table 3.5: FFTs Implemented on Processors [14]. AsAP has an estimated 1Ghz maximum clock frequency. FFTs Implemented on Processors. A "\*" indicates that the results are from simulations. A "\*\*" indicates a projection based on simulations.

### Chapter 4

### The AsAP DSP

The AsAP (Asynchronous Array of Simple Processors) [15] architecture is a parallel reconfigurable two-dimensional array of single-issue processors. Each processor has its own clock generation unit and can be configured to operate at a frequency different from its neighbors. Communication between neighbors is achieved by dual-clock FIFOs, since neighbor processors may have drastically varying clock frequencies. The entire AsAP has one or more 16-bit input ports and one or more 16-bit output ports. These ports are directly tied to individual processors in the array. Processors are pipelined with 16-bit fixed-point datapaths. Instructions for AsAP processors are 32-bits wide. Each AsAP processor has a 64-entry instruction memory and a 128-word data memory.

DSP algorithms are generally deterministic and don't rely on input data to make program flow decisions. For example, the number of iterations that a loop executes is usually pre-determined. In the same way, memory accesses are often pre-determined. Hardware designers can take advantage of such features when designing DSPs. To help with processing tasks that have complex (but deterministic) memory access patterns, each processor has four address generators that calculate addresses for data memory. Figure 4.1 is an overview of the key components in each AsAP DSP.

Figure 4.1: A block diagram for a single AsAP processor. Blocks labeled "DAG" represent data address generators.

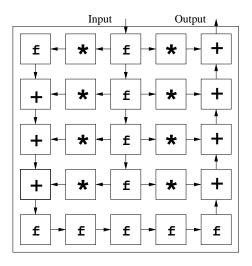

Figure 4.2: Dataflow for a fine-granularity 8-tap FIR filter. Processors marked "\*" execute multiplications. Processors marked "+" execute additions. Processors marked "f" forward data to other processors.

#### 4.1 Array Topology

Each processor in the array has two input FIFOs and one output port. Each input FIFO has 32 entries and can be connected to the output port of a neighbor processor. The choices for neighbor processor are north, south, west and east. Figure 4.2 shows an example interconnection network for an FIR filter. Since there are only two input FIFOs, there can be no more than two arrows pointing into a single processor. However, one processor can be the source of data for multiple processors. Since there is one output port, all the processors would receive the same data. The array topology of AsAP is well-suited for applications that are composed of a series of independent tasks. Each of these tasks can be assigned to one or more processors. As each processor is working on its task, the data that it needs becomes available at its input FIFO. Since data "flows" through the system, the dependence on a large global memory is reduced. Furthermore, an array of small high-throughput processors is more effective than single-datapath DSPs because multiple datapaths process different parts of the algorithm at the same time.

#### 4.2 Instruction Set

In an effort to make the AsAP instruction set architecture as simple as possible, the instruction format is fairly uniform. There is a 6-bit opcode field, an 8-bit destination field, two 8-bit source fields, and a 2-bit NOP field. The NOP field allows each instruction to specify up to 3 NOPs to execute after itself. These NOPs are used as a final resort if data dependencies cannot be alleviated by scheduling or bypass paths. There are four condition registers that specify whether the result of the instruction just executed is negative, has a carry-out, has overflowed, or is zero. Not all instructions affect these registers. Condition registers are used by branch instructions. AsAP instructions fall into 3 broad categories. Instructions that typically load one or two sources and use some part of the ALU or multiply unit are denoted "Type 1" instructions. Branch instructions are denoted "Type 2" instructions. The move immediate instruction is the only "Type 3" instruction. It is in a separate category because it has a single 16-bit source. Table 4.1 lists all instructions and their formats.

#### 4.3 Memories

There are four memories in each AsAP processor. 1) The instruction memory (IMem) is 32-bits wide, and has 64 entries. 2) The data memory (DMem) is 16-bits wide, and has 128 entries. Although many algorithms may require more of both types of memory, we hope that such algorithms can be divided and spread across multiple processors. The strategy in AsAP is to keep the size of each individual processor small so that more processors can reside in a fixed area. Configuration memory (CMem) is also 8-bits wide, and has only a handful of entries. 3) The configuration memory is composed of registers (not RAM), and holds static settings like input FIFO connect directions and local clock frequency. 4) The dynamic configuration memory (DCMem) is 16-bits wide and has 19 entries. DCMem is designed to hold configuration for parameters that can change during runtime. It primarily holds the constants that govern the operation of the address generators, which can change at runtime. DCMem also holds 4 loadable address pointers and a 4-bit output port configuration. A processor can write to any combination of the 4 possible

| Opcode             | Type | Dest | $\operatorname{Src1}$ | Src2 |

|--------------------|------|------|-----------------------|------|

| ADD, ADDH, ADDS    | 1    | х    | х                     | x    |

| ADDC, ADDCH, ADDCS | 1    | х    | х                     | x    |

| SUB, SUBH, SUBS    | 1    | х    | x                     | x    |

| SUBC, SUBCH, SUBCS | 1    | х    | х                     | x    |

| ADDINC, SUBINC     | 1    | х    | х                     | х    |

| MULTL, MULTH       | 1    | х    | х                     | x    |

| AND, NAND          | 1    | х    | х                     | x    |

| OR, NOR            | 1    | х    | х                     | x    |

| XOR, XNOR          | 1    | х    | х                     | х    |

| SHL, SHR           | 1    | х    | х                     | x    |

| SRA                | 1    | х    | х                     | x    |

| NOT                | 1    | х    | х                     |      |

| ANDWORD            | 1    | х    | х                     |      |

| ORWORD             | 1    | х    | х                     |      |

| XORWORD            | 1    | х    | х                     |      |

| MAC                | 1    | х    | х                     | х    |

| MACC               | 1    | х    | х                     | х    |

| ACCSHR, ACCSHL     | 1    |      | х                     |      |

| RPT                | 1    |      | х                     |      |

| BTRV               | 1    | х    | x                     |      |

| BRN, BRNN          | 2    |      |                       |      |

| BRC, BRNC          | 2    |      |                       |      |

| BRO, BRNO          | 2    |      |                       |      |

| BRZ, BRNZ          | 2    |      |                       |      |

| BRF0, BRF1, BROB   | 2    |      |                       |      |

| MOVI               | 3    | х    | х                     |      |

Table 4.1: Instruction Formats.

output directions, and this configuration can change at different points while the application runs.

#### 4.4 FIFOs

In AsAP, dual-clock FIFOs [16] are the core mechanism for communication between neighbor processors. Each FIFO has a 32-word (16-bit) circular buffer to hold data in transit. There are handshaking signals required between the FIFO and the entity that is attempting to get data from, or send data to the FIFO. For example, the FIFO has an output signal to let the sender know that there is no more space in the FIFO. Although all 32 words of the buffer may be occupied at some point, the FIFO will signal that the buffer is full before all 32 words are occupied. This is because there is a latency between the time that a FIFO signals full, and the time that the sender receives the signal and stops sending data. During that time, the remaining few entries are being filled. The number of buffer entries necessary to accommodate for latency is known as "reserve space."

Each dual-clock FIFO has a read side and a write side. Data arrives into the write side and is stored into the buffer. Data exits the FIFO on the read side. In AsAP processors, FIFOs are used as input ports. Therefore, the read side is interfaced to the local processor, and the write side is interfaced to an upstream processor. The upstream processor's clock signal is fed to the write side, along with other handshaking signals. The local processor's clock is fed to the read side, along with other handshaking signals. It is the responsibility of the FIFO to make sure that data is correctly transferred between these two different clock domains.

#### 4.5 Datapath and Pipeline

AsAP processors have a 9-stage pipeline which was designed with a RISC-style instruction set architecture in mind. At various locations in the pipeline, there are 16-bit bypass registers which can be used explicitly in instructions as sources. These bypass registers help alleviate the cycle penalties due to data dependence between instructions. In the AsAP pipeline, there is an instruction fetch stage, a decode stage, an operand fetch stage, a source select stage, three execute stages, a result select stage, and a memory write-back stage.

#### 4.6 Configuration

Each AsAP processor has a hard-coded processor number. This processor number is used to address the processor during configuration. Configuration (of IMem and CMem) is done via a global configuration bus. Each processor is responsible for "listening" on the configuration bus and determining if the data presented belongs to itself. If the data does belong to a particular processor, that processor is responsible for storing the data in the correct location. There is no handshaking on the configuration bus. The configuration bus consists of an address bus and a data bus. The address bus has a group of bits dedicated to selecting the processor, a groups of bits to select which memory is being written, and a group of bits to address a location in that memory. Also, there is a broadcast bit in the address bus, so that it is possible to configure all processors with the same value for some memory location.

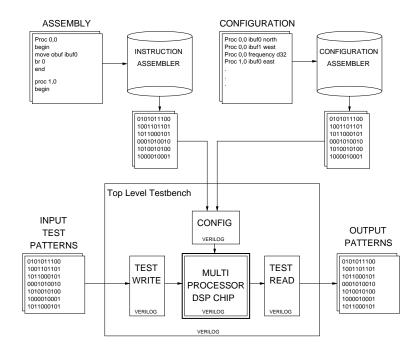

Applications that are mapped to AsAP and run on AsAP are referred to as "tests." For each test, there is a series of steps required to configure the AsAP chip and run the test. The first step in the process is to stop all processors from executing any code and to load CMem for each processor. The second step is to load and run (for each processor) programs that load useful constants into DMem or DCMem. The third and final step is to load the actual application program and allow it to run. For CMem, configuration parameters and their values are specified for each processor in a configuration file. Figure 4.3 is an example of a configuration file.

For DMem and DCMem, assembly code is assembled and loaded into IMem for each processor. This assembly code is allowed to run, so that the constants are loaded into DMem and DCMem. Figure 4.4 is an example of an assembly program that loads constants.

Finally, for IMem, the application assembly code is assembled and loaded into IMem for each processor. Figure 4.5 is an example of an unscheduled assembly program for

| # | ******        | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |   | * * * * * * * * * * * * * * * * * * * *       |  |

|---|---------------|---------------------|-----------------------------------------|---|-----------------------------------------------|--|

| # | proc **       | address **          | value *************                     | ( | comments ************************************ |  |

| # | * * * * * * * | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * | 1 | * * * * * * * * * * * * * * * * * * * *       |  |

|   |               |                     |                                         |   |                                               |  |

|   | 0,0           | ibuf0               | west                                    | # | input processor                               |  |

|   | 0,0           | frequency           | d7                                      | # | frequency                                     |  |

Figure 4.3: Sample configuration code for an application

```

begin 0,0

movi

dcmem 18

1

// obuf = s,w,n,e (east)

// dmem[0] = 0

dmem 0

0

movi

movi

dmem 70

64

// dmem[70] = 64

done:

// do nothing

done

br

end

```

Figure 4.4: Sample assembly code to load constants for an application

an application. An overall picture of the modules necessary for configuration and testing is shown in Fig. 4.6.

#### 4.7 Local Clock Generators

The local clock generator for each processor is digitally programmable. Normally, it is programmed once during configuration, and retains that clock frequency until it is re-configured. It is also "pausible," so that if a processor is idle for a long period of time, the clock no longer oscillates, which saves energy.

```

begin 0,0

start:

dmem 70

move

#0

// data_ctr = 0

brloop:

movi

dcmem 5

32512

// mask and=127, mask or=0

move

ag0

ibuf0

// get data from ibuf0

dcmem 5

dcmem 5

#1

// mask_and=127, mask_or=1

or

move

ag0pi

ibuf0

// get data from ibuf0

dmem 70

dmem 70

// data_ctr++

add

#1

sub

null

dmem 70

#32

// check if data_ctr = 32

brloop

// branch back if not done

brnz

// ****************** move data in

* * * * * * * * * * * * * * * * * *

#0

// aptr0 = 0

move

dcmem 0

outloop:

// obuf = dmem[aptr0]

move

obuf

aptr0

// aptr0 += 1

add

dcmem 0

dcmem 0

#1

dmem 71

sub

null

dcmem 0

// stop at 64

brnz

outloop

// branch back if not done

******** move data out ****************

// *****

br

start

end

```

Figure 4.5: Sample assembly code for an application. This code moves data from an input FIFO to DMem, then moves the data from DMem to OPort (obuf).

Figure 4.6: An overview of configuration and testing

### Chapter 5

### **Address Generation Hardware**

For algorithms with complex memory access patterns, address generators save processor cycles by pre-computing addresses. An address generator in AsAP is essentially a programmable pointer. Each processor has four address generators which can address any of the 128 words in data memory. An address generator can be used as the destination, source1, or source2 of an instruction word. When an instruction specifies an address generator as one of its sources, DMem uses the address from the address generator to fetch data. In the same manner, if the address generator is used as a destination, a write will occur to DMem, with the target address specified by the address generator.

#### 5.1 Address Generator Interface

Address generators can be used in two modes: normal and post-increment. In normal mode, the address output of the address generator does not advance. In postincrement mode, the address is advanced, but the new address is unavailable until the next clock cycle. For normal mode, the assembly-code names for the address generators are ag0, ag1, ag2, and ag3. The assembly-code names for post increment address generators are ag0pi, ag1pi, ag2pi, and ag3pi. Even though there are 8 names, there are still only four address generators.

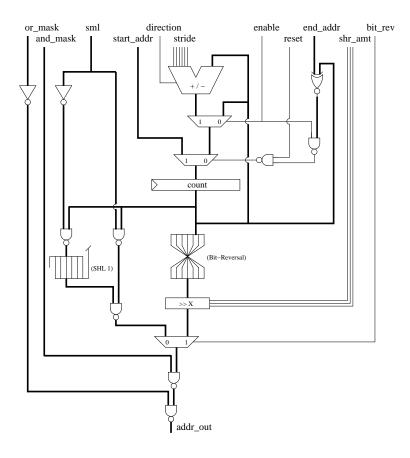

Each address generator has a set of inputs that dictate its memory access pattern. These inputs are: reset, enable, start\_addr, end\_addr, stride, direction, shr\_amt, bit\_rev, sml,

| Signal        | Word Width | Function                                               |

|---------------|------------|--------------------------------------------------------|

|               | (bits)     |                                                        |

| reset         | 1          | load <i>start_addr</i> into address generator          |

| enable        | 1          | allow add (or subtract) of stride to addr generator    |

| $start\_addr$ | 7          | start address                                          |

| $end\_addr$   | 7          | end address                                            |

| stride        | 6          | amount to increment or decrement address generator     |

| direction     | 1          | 1=increment, $0=$ decrement                            |

| $bit\_rev$    | 1          | reverse all 7 bits of address generator count register |

| $shr\_amt$    | 3          | shift right bit-reversed address up to 7 places        |

| sml           | 7          | split-mask-lo, mask used to split address for fft      |

| $and\_mask$   | 7          | generic AND mask                                       |

| $or\_mask$    | 7          | generic OR mask                                        |

Table 5.1: Address Generator Inputs

and\_mask, and or\_mask. Since AsAP's data memory has 128 words, addresses are seven bits wide. As such, most of the masks are seven bits. Table 5.1 describes the size and function of each address generator input.

Inside the address generator, there is a single seven-bit register that holds the current address. This register is referred to as the count register. The most fundamental decision made in the address generator is whether or not to advance the count register. The count register can only be advanced when the address generator is in post-increment mode (i.e. *enable* is asserted). If the *direction* input is asserted, then *stride* is added to the count register. Conversely, if the *direction* input is held low, *stride* is subtracted from the count register. The *bit\_rev* input is used to reverse the bits in the count register. The *shr\_amt* input shifts the bit reversed address right up to seven bits. The *bit\_rev* and *shr\_amt* inputs are commonly used to help generate addresses for FFT computation. Another input that is used for FFT computation is *sml* (split-mask-lo). Split-mask-lo is intended to take on the following values: "0000000", "0000001", "0000011", "0000111", "0001111", "0011111", "0111111", "Its functionality is discussed further in Section 5.2. The default value for *sml* is "1111111," so that its output is the unmodified count register. The last two inputs used are *and\_mask* and *or\_mask*. The default value for *and\_mask* is "1111111," so

Figure 5.1: Data Address Generator. Thin lines represent one-bit wires. Thick lines represent seven-bit wires.

that it does not change the address. The default value for *or\_mask* is "0000000," so that it does not change the address. These two masks are useful for restricting addresses to certain areas or blocks of the memory space.

#### 5.2 Address Generator Design

Each address generator is composed of a count register, an adder, multiplexers, a variable right shifter, and various logic gates. Figure 5.1 shows the design of the address generator. The seven-bit adder/subtracter is the most complex block in the address generator. The next most complicated blocks are the variable right shifter and the count register. The adder/subtracter is implemented with a simple adder and special logic that performs two's complement negation if subtraction is necessary. When the value of the count register is equal to the end address, or the *reset* signal is asserted, the count register is reloaded to

*start\_addr*. This is implemented with a multiplexer and some logic (including XNOR gates to compute equivalence).

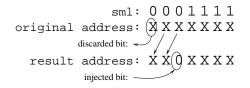

Below the count register, there are essentially two choices for the output address to take. Both are permutations of the count register. One of these choices is the bit-reverse path. The seven bits of the count register are reversed, then shifted right by *shr\_amt*. The variable shift amount allows bit reversal to be useful for FFTs of varying length (with an upper limit of seven-bit addresses). The second choice for the output is the split-mask-lo path. Addresses for points in the FFT have a single bit "injected" into the address at different bit-positions (depending on the stage in the FFT). Split-mask-lo is a binary mask, which in its simplest form is a string of 0's followed by a string of ones. Figure 5.2 shows how the split-mask-lo is applied to an input signal so that the result has an injected bit.

Figure 5.2: Example of Split-Mask-Lo Operation

The new bit is added at the boundary between a string of zeros and a string of ones in *sml*. The binary value of the inserted bit is zero. This can be changed further in the address generator with *or\_mask*. The multiplexer that selects the signal from either the bit-reverse path or the split-mask-lo path is controlled by a single bit input, *bit\_rev*. If neither of these two permutations is needed, and just the count register is desired, then *bit\_rev* should be set to 0 and *sml* should be set to "1111111." The hardware is designed so that the output is simply the count register when *sml* is "1111111." The final modifications that can be made to the address in the count register are the *and\_mask* and *or\_mask*. First, the seven-bit *and\_mask* is applied to the signal from the multiplexer. This is normally used to force some or all of the bits in the address to zeros. After that, the *or\_mask* is applied, which allows any of the seven bits to be set to one.

The address generator is designed to reside in one to two pipeline stages in a pipelined processor. The internal count register can be treated as one of the pipeline registers that separates stages. The logic above the count register is likely to be in the same stage that instructions are decoded. The logic after the count register can be fed directly into a memory, but this is unlikely because a memory will probably have more addressing modes than just address generators. For this reason, the logic after the count register, in combination with multiplexers that select the addressing mode, will be in another pipeline stage. With these requirements taken into account, address generators were integrated into AsAP.

### Chapter 6

### Mapping FFTs on to AsAP

Mapping algorithms to the AsAP DSP is a two-phase process. First, the programmer must decide how to partition the algorithm so that it can be distributed over multiple processors in AsAP. This is assuming the algorithm is complex enough that it needs more resources than one AsAP processor. Second, the programmer must write and test assembly code for each active processor in the array, to implement the entire algorithm. How much effort each of these phases receives has great impact on factors such as performance, power consumption, energy usage and processor utilization. There are various trade-offs between pairs or groups of these factors.

The first model of AsAP is implemented in Verilog HDL. This model is a singlecycle behavioral model of the processor array, including FIFOs and configuration hardware. Since the model does not describe the pipelined version of AsAP, hazards due to data dependencies and structural conflicts are not apparent. The code presented does not include any scheduling details.

#### 6.1 Using Address Pointers and Address Generators

Address pointers and address generators provide the AsAP programmer with an indirect way to access memory. They are pointers in the programming language sense of the word; when de-referenced, they fetch data from data memory using the address they currently hold. When an AsAP programmer wishes to de-reference an address pointer or

|      | BIT | 15         | 14 | 13 | 12   | 11     | 10   | 9   | 8        | 7 | 6        | 5      | 4   | 3             | 2     | 1             | 0  |               |     |

|------|-----|------------|----|----|------|--------|------|-----|----------|---|----------|--------|-----|---------------|-------|---------------|----|---------------|-----|

| ADDR | ESS |            |    |    |      |        |      |     |          |   |          |        |     |               |       |               |    |               |     |

|      | 0   |            |    |    | addr | ess pi | r 1  |     |          |   |          |        | add | ress p        | otr O |               |    |               |     |

|      | 1   |            |    |    | addr | ess pi | er 3 |     |          |   |          |        | add | ress p        | otr 2 |               |    |               |     |

|      | 2   |            | _  |    |      |        |      |     |          |   | BR       | DIR    |     |               |       | SHR_AM        | IT | $\square$     |     |

|      | 3   |            |    |    | ST   | ART_A  | DDR  |     |          |   |          |        | E   | ND_ADI        | DR    |               |    | ](            | DAG |

|      | 4   |            |    |    |      | STR    | IDE  |     |          |   |          |        |     | SML           |       |               |    |               | DAG |

|      | 5   |            |    |    | M    | ASK_AN | ID   |     |          |   |          |        | 1   | ASK_0         | R     |               |    | $\mathcal{V}$ |     |

|      | 6   |            |    |    |      |        |      |     |          |   | BR       | DIR    |     |               | 2     | SHR_AM        | IT |               |     |

|      | 7   |            |    |    | ST   | ART_A  | DDR  |     |          |   | END_ADDR |        |     | ](            | DAG   |               |    |               |     |

|      | 8   |            |    |    |      | STR    | IDE  |     |          |   | SML      |        |     |               | DAG   |               |    |               |     |

|      | 9   |            |    |    | M    | ASK_AN | ID   |     |          |   | MASK_OR  |        |     | $\mathcal{V}$ |       |               |    |               |     |

| 1    | LO  |            |    |    |      |        |      |     |          |   | BR       | DIR    |     |               | 2     | SHR_AM        | IT |               |     |

| 1    | 11  |            |    | -  | ST   | ART_A  | DDR  |     |          |   | END_ADDR |        |     | ](            | DAG   |               |    |               |     |

| 1    | L2  |            |    |    |      | STR    | IDE  |     |          |   |          |        |     | SML           |       |               |    |               | DAG |

| 1    | L3  |            |    |    | M    | ASK_AN | ID   |     |          |   |          |        | 1   | ASK_0         | R     |               |    | $\mathcal{V}$ |     |

| 1    | L4  |            |    |    |      |        |      |     |          |   | BR       | DIR    |     |               |       | SHR_AM        | IT |               |     |

| 1    | L5  | START_ADDR |    |    |      |        |      |     | END_ADDR |   |          | ](     | DAG |               |       |               |    |               |     |

| 1    | L6  | STRIDE     |    |    |      |        |      | SML |          |   |          | DAG    |     |               |       |               |    |               |     |

| 1    | L7  | MASK_AND   |    |    |      |        |      |     |          |   | 1        | MASK_O | R   |               |       | $\mathcal{V}$ |    |               |     |

| 1    | L8  |            |    |    |      |        |      |     |          |   |          |        |     |               | OBU   | F_CFG         |    |               |     |

Figure 6.1: DCMem Map. Shaded addresses are not used. "BR" = bit-reverse, "DIR" = direction, "SML" = split-mask-lo, "SHR\_AMT" = shift right amount

address generator, the normal names are used (aptr0,aptr1,aptr2,aptr3,ag0,ag1,ag2,ag3). When the programmer wants to change where the pointer is pointing to, changes must be made to DCMem. Figure 6.1 shows all the fields in DCMem.

#### 6.1.1 Address Pointers

Each AsAP processor has four address pointers in addition to its four address generators. Address pointers are seven-bit registers that are mapped into DCMem. When the field for an address pointer in DCMem is set to a particular value, the corresponding address pointer can be used as a source or destination. The following lines of assembly code are an example of how to use address pointers.

| movi | dcmem 0 | 15    |

|------|---------|-------|

| move | obuf    | aptr0 |

The first line loads DCMem[0] with "15," so that aptr0 points to DMem[15]. The second line uses aptr0 to access DMem (using the address 15) and moves the contents to the OPort (also referred to as "obuf"). Since aptr0 and aptr1 are in the same memory word, writing

a value to DCMem[0] overwrites the value for both pointers.

#### 6.1.2 Address Generators

Configuring the address generators is similar to loading the address pointers. Modifying values in DCMem changes the behavior of the address generator. The following lines of assembly code are an example of how to use address generators.

| movi | dcmem 2 | 32    | <pre>// ag0 br=0, dir=1, shr_amt=0</pre> |

|------|---------|-------|------------------------------------------|

| movi | dcmem 3 | 269   | <pre>// ag0 start=1, end=13</pre>        |

| movi | dcmem 4 | 895   | // ag0 stride=3, sml=1111111             |

| movi | dcmem 5 | 32512 | // ag0 and_mask=1111111                  |

|      |         |       | // ag0 or_mask=0000000                   |

| rpt  | #10     |       | <pre>// rpt next line 10 times</pre>     |

| move | obuf    | ag0pi | // move to obuf DMem[ag0]                |

The first four lines move constants into DCMem to configure ag0. This address generator is programmed to cycle through the following addresses: 1, 4, 7, 10, 13. After the address generator reaches 13, the next address automatically returns to 1. This is because *start\_addr* is set to 1 and *end\_addr* is set to 13. The repeat instruction causes the move instruction to execute 10 times. The move instruction dereferences the address generator and moves the data from DMem to the output port.

The programmer must make sure that the count register is the same as  $end\_addr$  at some point in order to restart the sequence. If  $end\_addr$  and the count register never match, the output will continue past 13. In the above case, the count register and the output address are identical, but there are cases where they are not the same. An example of such a case is if the  $and\_mask$  were set to "1111110." The output sequence would then be: 0, 4, 6, 10, 12. The count register would still cycle through the original sequence (1, 4, 7, 10, 13). If the programmer wants the address generator to restart at 0 after 12, then the  $end\_addr$  should be set to 13, because that is the value in the count register that corresponds to the end of the sequence.

It is possible to achieve the same results by simply using address pointers in a controlled loop. This will be less code than the amount necessary to configure and use address generators. However, using the address generators can speed up the execution of code dramatically. Instead of wasting cycles incrementing the address pointer to calculate the next address and checking bounds, the move instruction can be executed repeatedly with nearly no loop overhead. This is a trade-off between instruction memory (IMem) space and performance.

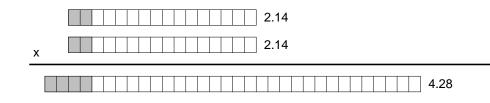

## 6.2 Butterflies

Radix-2 butterflies are implemented in fixed-point 2.14 notation on AsAP, for reasons discussed later in this section. In 2.14 notation, the two most significant bits represent the integer part of the number, and the 14 least significant bits represent the fractional portion. Fixed-point numbers can be treated just like integers, but it is the programmer's responsibility to keep track of how the decimal point shifts between computations. The algorithm for computing a butterfly is the same for all FFTs with lengths that are a power of two. Therefore, the assembly code for the butterfly is reusable. Equations 6.1 and 6.2 are the definition of a radix-2 butterfly. Figure 2.1 is a visual description of the butterfly.

$$A_{m+1} = A_m + W_N^r B_m \tag{6.1}$$

$$B_{m+1} = A_m - W_N^r B_m \tag{6.2}$$

Equations 6.3 and 6.4 are the same definition, but with simplified notation.

$$A^+ = A + WB \tag{6.3}$$

$$B^+ = A - WB \tag{6.4}$$

Since this is implemented on a computer that does not have inherent capabilities to process complex numbers, the real and imaginary parts of each point are treated as separate 16-bit integers. Equations 6.5 and 6.6 show both the real and imaginary components of the points.

$$A_r^+ + jA_i^+ = A_r + jA_i + (W_r + jW_i)(B_r + jB_i)$$

(6.5)

$$B_r^+ + jB_i^+ = A_r + jA_i - (W_r + jW_i)(B_r + jB_i)$$

(6.6)

Now, the 4 inputs  $(A_r, B_r, A_i, B_i)$ , and the 4 outputs  $(A_r^+, B_r^+, A_i^+, B_i^+)$  of the butterfly can easily be distinguished. After some simplification, the equations for each of the outputs

becomes apparent.

$$A_r^+ + jA_i^+ = A_r + jA_i + (W_r B_r - W_i B_i + j(W_i B_r + W_r B_i))$$

(6.7)

$$B_r^+ + jB_i^+ = A_r + jA_i - (W_r B_r - W_i B_i + j(W_i B_r + W_r B_i))$$

(6.8)

$$A_r^+ + jA_i^+ = A_r + (W_r B_r - W_i B_i) + j(A_i + (W_i B_r + W_r B_i))$$

(6.9)

$$B_r^+ + jB_i^+ = A_r - (W_r B_r - W_i B_i) + j(A_i - (W_i B_r + W_r B_i))$$

(6.10)

$$A_r^+ = A_r + (W_r B_r - W_i B_i) \tag{6.11}$$

$$B_r^+ = A_r - (W_r B_r - W_i B_i) ag{6.12}$$

$$A_i^+ = A_i + (W_i B_r + W_r B_i) \tag{6.13}$$

$$B_i^+ = A_i - (W_i B_r + W_r B_i) \tag{6.14}$$

Equations 6.11 and 6.12 show that  $A_r^+$  and  $B_r^+$  have a common term. This means we can save computation by computing it only once. A similar common term exists for Equations 6.13 and 6.14.

The preferable format to store all these values is in 1.15 notation, because full range for twos complement 1.15 notation is [-1.0, 0.99997], which is easy to understand. Unfortunately, storage in 1.15 is undermined by twiddle factors. In the complex plane, twiddle factors have varying angles, but always have a magnitude of one. The range for the real and imaginary components of twiddle factors is therefore [-1.0, 1.0]. Either some of the twiddle factors would be incorrect by a small value, or a different notation needs to be used. In fact, the zero twiddle factor ( $W_N^r$  where r = 0), which is the most common in FFTs, corresponds to the value 1.0. We chose to implement a different notation (2.14) so that we could fully represent such twiddle factors with no error. One side effect is that some accuracy is lost for very small numbers, because there is one less bit representing the fractional component of the complex number. The range of a 2.14 fixed-point number is [-2.0, 1.99994].

When two fixed-point numbers are multiplied by each other, the result is not in the same format as the inputs. In a 16-bit computer, the product is 32 bits. Since memory words in AsAP are 16 bits, and we do not want to the width of data to grow through

Figure 6.2: A 16-bit multiplication. Shaded bits denote the integer portion of the number.

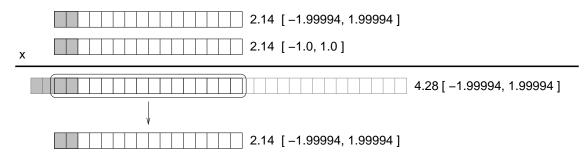

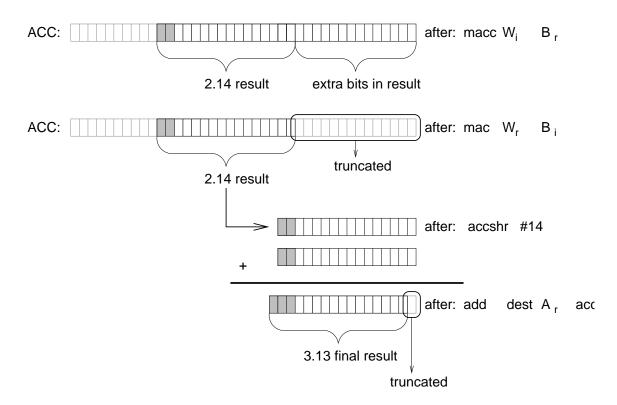

stages of computation, we will need to discard 16 bits. Normally, the upper 16 bits are saved, and the lower 16 are discarded. This is because the upper 16 bits contain the most significant information about the number. Figure 6.2 shows a multiplication between two 2.14 fixed-point numbers, and the format of the product. In AsAP, there are two multiply instructions. The "MULTL" instruction executes a multiply and uses the lowest 16 bits of the product as the result. The "MULTH" instruction uses the upper 16 bits of the product as the result. The only multiplies between numbers AsAP FFTs are between a twiddle factor and a point. The magnitude of a twiddle factor is never larger than 1.0. If the magnitude of a point is restricted to the range [-1.99994, 1.99994], then the product of a twiddle factor and a point is guaranteed to have the range [-1.99994, 1.99994]. This is convenient because it can be represented with 2.14 notation. However, the upper two bits and lower 14 bits of the product need to be discarded. This cannot be accomplished with "MULTL" or "MULTH" instructions. Instead, the accumulator is used. A "MAC" instruction, followed by an "ACCSHR" (accumulator shift right) instruction can accomplish the task. Figure 6.3 shows which bits are actually used in the multiplication.

Figure 6.3: A special fixed-point multiply. Since the twiddle factor has a maximum magnitude of 1, the signal does not grow through multiplication. The upper 2 bits and lower 14 bits can be discarded.

Figure 6.4: FFT Butterfly Error

It is convenient that the multiplies in the butterfly do not cause signal growth. There is no way to avoid signal growth when additions or subtractions are done. Equations 6.3 and 6.4 show that the largest signal growth in a butterfly is a factor of two. Therefore, when performing additions or subtractions for the butterfly, the "ADDH", and "SUBH" instructions should be used. However, we would like to round on additions and subtractions. Rounding will help to reduce the error induced by each computation. The "ADDH" and "SUBH" instructions both make use of truncation. Once two 16-bit numbers are added to each other or subtracted, the lowest bit of the 17-bit result is discarded. On average, the value of the (truncated) 16-bit number is 1/2 lsb (least significant bit) less than the actual result. Calculating the butterfly is more complicated than simply compensating for this bias because the accumulator is used, and bits are truncated twice. Figure 6.4 shows the step-by-step computation of Eq. 6.13. The value of the accumulator is shown after each computation has completed.

The first truncation results in a net bias of -1/2 lsb in the result. The second