### **Power Estimation**

## Welcome

- If you are new to FPGA design, this module will help you estimate your FPGA power consumption

- These design techniques promote fast and efficient FPGA design development

# After completing this module, you will able to:

- List the three phases of the design cycle where power calculations can be performed

- Estimate power consumption by using the XPower Estimator spreadsheet

- Estimate power consumption by using the XPower software utility

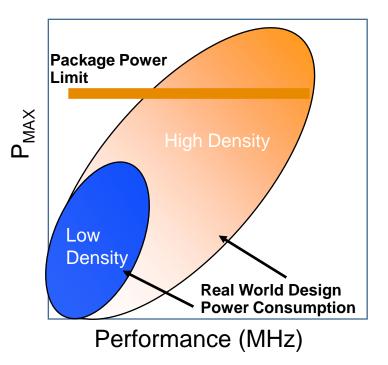

## **Power Consumption Overview**

- As devices get larger and faster, power consumption goes up

- First-generation FPGAs had

- Lower performance

- Lower power requirements

- No package power concerns

- Today's FPGAs have

- Much higher performance

- Higher power requirements

- Package power limit concerns

- A System Monitor that provides active monitoring of the die temperature

- Refer to the Virtex-6 User Guide for more information

## **Power Consumption Concerns**

- High-speed and high-density designs require more power, leading to higher junction temperatures

- Package thermal limits exist

- > 125° C for plastic

- 150° C for ceramic

- Power directly limits

- > System performance

- Design density

- Package options

- Device reliability

## **Estimating Power Consumption**

**Estimating power consumption is a complex calculation**

- > Power consumption of an FPGA is almost exclusively dynamic

- Power consumption is dependent on design and is affected by

- Output loading

- System performance (switching frequency)

- Design density (number of interconnects)

- Design activity (percent of interconnects switching)

- Logic block and interconnect structure

- Supply voltage

## **Estimating Power Consumption**

- Power calculations can be performed at three distinct phases of the design cycle

- Concept phase: A rough estimate of power can be calculated based on estimates of logic capacity and activity rates

- Use the Xilinx Power Estimator spreadsheet

- <u>Design phase</u>: Power can be calculated more accurately based on detailed information about how the design is implemented in the FPGA

- · Use the XPower Analyzer

- System Integration phase: Power is calculated in a lab environment

- Use actual instrumentation

- Accurate power calculation at an early stage in the design cycle will result in fewer problems later

## **Activity Rates**

- Accurate activity rates (also known as toggle rates) are required for meaningful power calculations

- Clocks and input signals have an absolute frequency

- Synchronous logic nets use a percentage activity rate

- > 100% indicates that a net is expected to change state on every clock cycle

- Allows you to adjust the primary clock frequency and see the effect on power consumption

- Can be set globally to an average activity rate on groups or individual nets

- Logic elements also use a percentage activity rate

- Based on the activity rate of output signals of the logic element

- Logic elements have capacitance

**Excel** spreadsheets with power estimation formulas built in

- > Enter design data in white boxes

- Power estimates are shown in gray boxes

Sheets

- Summary (device totals)

- > Clock, Logic, I/O, Block RAMs, DSP, MMCM

- > GTX, TEMAC, PCIE

- To download go to <u>http://www.support.xilinx.com</u>-> Technology Solutions -> Power

- Download the XPE spreadsheet for your device family

- XPE is not installed with the ISE software

- > The Power Solutions page has numerous resources

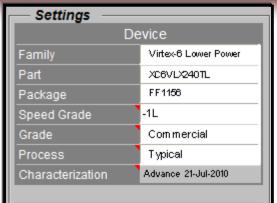

#### Summary and Quiescent power

- White boxes allow you to enter design data

- <u>Gray</u> boxes show you the Power estimates

- Tabs at bottom allow you to enter power information per device resources (not shown)

- <u>Settings</u> reviews device, system, and environment information

- <u>On-Chip Power</u> breaks the estimated power consumption into device resources

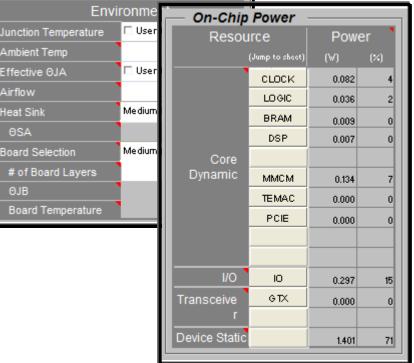

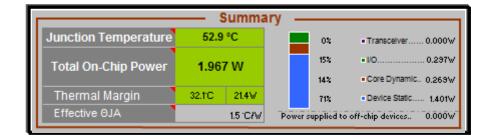

#### Summary and Quiescent power

- <u>Power Supply</u> reviews what power sources will be necessary

- <u>Summary</u> describes your systems total power and estimated junction temperature

| — Power Supply ———  |         |       |  |  |  |  |  |  |  |

|---------------------|---------|-------|--|--|--|--|--|--|--|

| Source              | Voltage | Total |  |  |  |  |  |  |  |

| Jource              | (V)     | All   |  |  |  |  |  |  |  |

| V <sub>ссінт</sub>  | 0.900   | 1.304 |  |  |  |  |  |  |  |

| Vccaux              | 2.500   | 0.195 |  |  |  |  |  |  |  |

|                     |         |       |  |  |  |  |  |  |  |

| Vcco 2.5            | 2.500   | 0.112 |  |  |  |  |  |  |  |

| Vcco 1.8            | 1.800   | 0.000 |  |  |  |  |  |  |  |

| Vcco 1.5            | 1.500   | 0.000 |  |  |  |  |  |  |  |

| Vcco 1.2            | 1.200   | 0.000 |  |  |  |  |  |  |  |

| MGTAVec             | 1.000   | 0.000 |  |  |  |  |  |  |  |

| MGTAV <sub>TT</sub> | 1.200   | 0.000 |  |  |  |  |  |  |  |

| •                   |         |       |  |  |  |  |  |  |  |

| •                   |         |       |  |  |  |  |  |  |  |

|                     |         |       |  |  |  |  |  |  |  |

|                     |         |       |  |  |  |  |  |  |  |

| •                   |         |       |  |  |  |  |  |  |  |

|                     |         |       |  |  |  |  |  |  |  |

| Name    | Frequency<br>(MHz) | Туре   | Fanout | Clock<br>Buffer<br>Enable | Slice<br>Clock<br>Enable | Power<br>(W) |

|---------|--------------------|--------|--------|---------------------------|--------------------------|--------------|

| clock_a | 100.0              | Global | 1000   | 100%                      | 50%                      | 0.010        |

| clock_b | 200.0              | Global | 1000   | 100%                      | 50%                      | 0.020        |

| clock_c | 250.0              | Global | 4000   | 100%                      | 50%                      | 0.053        |

|         | 0.0                | Global | 0      | 100%                      | 50%                      | 0.000        |

#### Logic power

| Name            | Clock<br>(MHz) | Logic | LUTs as<br>Shift<br>Registers | Distributed<br>RAMs | FFs  | Toggle<br>Rate | Average<br>Fanout | Power<br>(W) |

|-----------------|----------------|-------|-------------------------------|---------------------|------|----------------|-------------------|--------------|

| ctrl_block      | 200.0          | 2000  | 100                           | 100                 | 2000 | 12.5%          | 3.00              | 0.023        |

| messenger_block | 100.0          | 1000  | 0                             | 0                   | 1000 | 12.5%          | 3.00              | 0.005        |

| state_machine   | 250.0          | 150   | 0                             | 0                   | 1250 | 12.5%          | 3.00              | 0.008        |

|                   | I/O Settings            |   |                 |   |                    |          | Activity Outo   |       |       |              | Outpu           | On Chip Power (W) |                            |                            |                               |

|-------------------|-------------------------|---|-----------------|---|--------------------|----------|-----------------|-------|-------|--------------|-----------------|-------------------|----------------------------|----------------------------|-------------------------------|

| Name              | I/O Standard            |   | Outpu<br>t Pins |   | IO LOGIC<br>SERDES | IO DELAY | IBUF LOV<br>PVR |       |       | Data<br>Rate | Output<br>Enabl | t Load<br>(pF)    | V <sub>CCINT</sub><br>0.9V | V <sub>CCAUX</sub><br>2.5V | V <sub>CCO</sub><br>all rails |

| control_outputs   | LVCMOS 2.5V 12mA (Slow) | 0 | 80              | 0 | No                 | Off      | Yes             | 100.0 | 12.5% | SDR          | 100.0%          | 0                 | 0.001                      | 0.004                      | 0.062                         |

| processor_outputs | LVCMOS 2.5V 12mA (Slow) | 0 | 50              | 0 | No                 | Off      | Yes             | 150.0 | 12.5% | SDR          | 100.0%          | 0                 | 0.001                      | 0.004                      | 0.058                         |

| communicator      | LVCMOS 2.5V 12mA (Slow) | 0 | 100             | 0 | No                 | Off      | Yes             | 200.0 | 12.5% | SDR          | 100.0%          | 0                 | 0.002                      | 0.011                      | 0.155                         |

#### Block RAM, DSP, and MMCM power

| Name          | BRAMs | Mode   | Toggl<br>e Rate |       | Enabl<br>e Rate |   | Write Mode  |       |     | Enabl<br>e Rate | Bit<br>Width | Write Mode  | Write<br>Rate | Power<br>(W) |

|---------------|-------|--------|-----------------|-------|-----------------|---|-------------|-------|-----|-----------------|--------------|-------------|---------------|--------------|

| memory_bank_a | 6     | RAMB18 | 50.0%           | 100.0 | 25.0%           | 1 | WRITE_FIRST | 50.0% | 0.0 | 25.0%           | 1            | WRITE_FIRST | 50.0%         | 0.001        |

| memory_bank_b | 10    | RAMB18 | 50.0%           | 150.0 | 25.0%           | 1 | VRITE_FIRST | 50.0% | 0.0 | 25.0%           | 1            | WRITE_FIRST | 50.0%         | 0.003        |

| memory_bank_c | 10    | RAMB18 | 50.0%           | 200.0 | 25.0%           | 1 | WRITE_FIRST | 50.0% | 0.0 | 25.0%           | 1            | WRITE_FIRST | 50.0%         | 0.004        |

| Name       | DSP<br>Slices | Clock<br>(MHz) | Toggle<br>Rate | MREG<br>Used? | MULT<br>Used? | Pre-add<br>Used? | Power<br>(W) |

|------------|---------------|----------------|----------------|---------------|---------------|------------------|--------------|

| Filter     | 4             | 250.0          | 12.5%          | Yes           | Yes           | No               | 0.003        |

| Transform  | 4             | 200.0          | 12.5%          | Yes           | Yes           | No               | 0.002        |

| Multiplier | 6             | 100.0          | 12.5%          | Yes           | Yes           | No               | 0.002        |

| Name    | Clock<br>(MHz) | Phase<br>Shift | Divide<br>Counte | Multiply<br>Counte | Clock 0<br>Divide | Clock 1<br>Divide | Clock 2<br>Divide | Clock 3<br>Divide | Clock 4<br>Divide | Clock 5<br>Divide | Clock 6<br>Divide | V <sub>CCINT</sub><br>(W) | V <sub>CCAUX</sub><br>(W) |

|---------|----------------|----------------|------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|---------------------------|

| clock_a | 100.0          | None           | 1                | 2                  | off               | 0.001                     | 0.044                     |

| clock_b | 150.0          | None           | 1                | 1                  | off               | 0.001                     | 0.042                     |

| clock_c | 200.0          | None           | 1                | 1                  | off               | 0.001                     | 0.045                     |

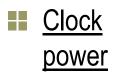

#### **Graphs**

## What is the XPower Analyzer?

- A utility for estimating the power consumption and junction temperature of FPGA and CPLD devices

- **Reads** an implemented design (NCD file) and timing constraint data

- You supply activity rates

- Clock frequencies

- Activity rates for nets, logic elements, and output pins

- Capacitive loading on output pins

- Power supply data and ambient temperature

- Detailed design activity data from simulation (VCD file)

- The XPower Analyzer calculates the total average power consumption and generates a report

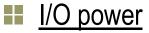

## **Running the XPower Analyzer**

- Expand Implement Design → Place & Route

- Double-click XPower Analyzer to launch the XPower utility in interactive mode

- Use the Generate Power Data process to create reports using VCD files or TCL scripts

| 🔤 Process Properties - XPower Analyzer Properties |         |  |  |  |  |  |  |

|---------------------------------------------------|---------|--|--|--|--|--|--|

| Property Name                                     |         |  |  |  |  |  |  |

| Load Physical Constraints File                    | Default |  |  |  |  |  |  |

| Load Setting File                                 |         |  |  |  |  |  |  |

| Load Simulation File                              | Default |  |  |  |  |  |  |

| Other XPower Analyzer Command Line Options        |         |  |  |  |  |  |  |

### Summary

| File View Tools Help       |                      |                          |      |                 |                 |

|----------------------------|----------------------|--------------------------|------|-----------------|-----------------|

| 🖻 🖥 🖉 🖉 🔁                  |                      |                          |      |                 |                 |

| eport Navigator            | × Name               | Value                    | Used | Total Available | Utilization (%) |

| iew                        | Clocks               | 0.00000 (W)              | 1    |                 |                 |

| Report Views               | Logic                | 0.00000 (W)              | 8    | 46560           | 0.1             |

| 🗐 试 Summary                | Signals              | 0.00000 (W)              | 305  |                 |                 |

| Thermal Information        | IOs 🛛                | 0.00000 (W)              | 211  | 220             | 95.9            |

| Voltage Source Information | DSPs                 | 0.00000 (W)              | 3    | 288             | 1.0             |

| Settings                   |                      |                          |      |                 |                 |

| 🖃 🌆 By Type                | Total Quiescent Powe | 0.77951 (W)              |      |                 |                 |

| Clocks                     | Total Dynamic Power  | 0.00000 ( <del>W</del> ) |      |                 |                 |

|                            | Total Power          | 0.77951 ( <del>V</del> ) |      |                 |                 |

| ⊡ Signals                  |                      |                          |      |                 |                 |

| Data                       | Junction Temp        | 53.4 (degrees C)         |      |                 | l               |

|                            |                      |                          |      |                 |                 |

| DSPs                       |                      |                          |      |                 |                 |

- **Estimated junction temperature**

- **Reporting**, settings, and thermal information is all placed in one utility

- > As you manipulate system characteristics you will update the generated report

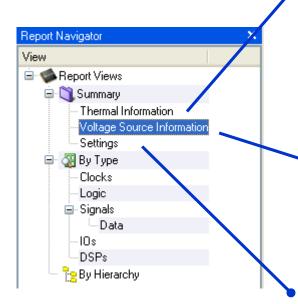

- Report Navigator allows for quick migration to various reports and functions of the utility

### **Report Navigator**

| Name                            | Value                | Range       |

|---------------------------------|----------------------|-------------|

| Ambient Temp (degrees C)        | 60.0                 | 0.0 to 85.0 |

| User Junction Temp (degrees C)  |                      |             |

| Use custom ThetaJA ?            | No 💌                 |             |

| Custom ThetaJA (degrees C/W)    | NA                   |             |

| Airflow (LFM)                   | 250 💌                |             |

| Heat Sink                       | None 💌 💌             |             |

| Custom ThetaSA (degrees C/W)    | NA                   |             |

| Board Selection                 | Medium (10''x10'') 💌 |             |

| # of Board Layers               | 8 to 11 🛛 💌          |             |

| Custom ThetaJB (degrees C/W)    | NA                   |             |

| Board Temperature (degrees C)   | NA                   |             |

|                                 |                      |             |

| Effective ThetaJA (degrees C/W) | 6.5                  |             |

| Max Ambient (degrees C)         | 77.8                 |             |

| Junction Temp (degrees C)       | 67.2                 |             |

## Thermal Information

## Voltage Source

| Name   | Power (W) | Voltage | Range          | Icc (A) | loog (A) |

|--------|-----------|---------|----------------|---------|----------|

| Vecint | 0.66451   | 1.000   | 0.950 to 1.050 | 0.00000 | 0.66451  |

| Vecaux | 0.11250   | 2.500   | 2.375 to 2.625 | 0.00000 | 0.04500  |

| Vcco25 | 0.00250   | 2.500   | 2.380 to 2.630 | 0.00000 | 0.00100  |

| Name                 | Value            | Range            |

|----------------------|------------------|------------------|

| FF Toggle Rate (%)   | 15.0             | 0.0 to 200.0     |

| 1/0 Toggle Rate (%)  | 15.0             | 0.0 to 200.0     |

| Output Load (pF)     | 5.0              | 0.0 to 1000000.0 |

| 1/0 Enable Rate (%)  | 100.0            | 0.0 to 100.0     |

| BRAM Write Rate (%)  | 50.0             | 0.0 to 100.0     |

| BRAM Enable Rate (%) | 25.0             | 0.0 to 100.0     |

| DSP Toggle Rate (%)  | 12.5             | 0.0 to 200.0     |

|                      |                  |                  |

| Part                 | xc6vlx75tff484-1 |                  |

| Package              | ff484            |                  |

| Grade                | Commercial 💌     |                  |

| Process              | Typical          |                  |

- **Settings**

- Each box is color coded

## **Advanced Report**

#### **Produced** as a simple text file

- File is given .pwr extension

- Report is more detailed and stored in one text file

- Some what-if analysis information is included

- Includes a Power Improvement Guide

| Power summary                     | Ι     | I (mA) | Ι    | P(mW)   | Ι   |

|-----------------------------------|-------|--------|------|---------|-----|

| Total estimated power consumption |       |        | I    | 779.51  | I   |

| Total Vccint 1.00V                | r 1   | 664.51 | 1    | 664.51  | I   |

| Total Vccaux 2.50V                | r i - | 45.00  | i    | 112.50  | i   |

| Total Vcco25 2.50V                | r i   | 1.00   | i    | 2.50    | i   |

| Clocks                            | 1     |        | 1    | 0.00    | 1   |

| DSP                               | 1     |        | 1    | 0.00    | 1   |

| IO                                | 1     |        | I.   | 0.00    | 1   |

| Logic                             | 1     |        | 1    | 0.00    | 1   |

| Signals                           | Ι     |        | Ι    | 0.00    | I   |

| Quiescent Vccint 1.00V            | , I   | 664.51 | 1    | 664.51  | I   |

| Quiescent Vccaux 2.50V            | r i - | 45.00  | i    | 112.50  | i   |

| Quiescent Vcco25 2.50V            | r i   | 1.00   | Ì    | 2.50    | İ   |

| Package power limits, ambient 50C | T     |        | T    | 1891.89 | I   |

| 250 LFM                           | 1     |        | 1    | 2713.18 | 1   |

| 500 LFM                           | 1     |        | 1    | 3070.18 | 1   |

| 750 LFM                           | I     |        | Ι    | 3333.33 | I   |

| Thermal summary                   |       |        |      |         |     |

| Estimated junction temperature    |       |        | 53C  |         | 1   |

| 0 airflow of 250 LFM              | Í.    |        | 53C  |         | Ì   |

| 500 LFM                           | 1     |        | 53C  |         | 1   |

| 750 LFM                           | Í.    |        | 53C  |         | - i |

| Ambient temp                      | Í.    |        | 50C  |         | Ì   |

| Case temp                         | 1     | 53C    |      |         | Ì   |

| Theta J-A                         | i.    |        | 4C/1 | J       | - I |

|                                   |       |        |      |         |     |

| Max ambient at junction max of    | 1     | 85C    | 1    | 82C     | I   |

| 250 LFM                           | 1     |        | 82C  |         | I   |

| 500 LFM                           | 1     |        | 82C  |         | - 1 |

| 750 LFM                           | 1     |        | 82C  |         | 1   |

## What Next?

- If you have a problem with your thermal budget there are many things you can consider

- > Determine which components in your design are using the most power

- Try to use as much of the dedicated hardware as possible

- Review the Power Improvement Guide section in the Advanced Power Report

- Evaluate your activity rates

- Reduce excess signal power or excess device utilization

- Synthesis options

- Implementation tool options

- HDL code

- Reduce excess static power

- Adjust the external environment

### Summary

- Power calculations can be performed at three distinct phases of the design cycle

- Concept phase: (Power Estimator spreadsheet)

- Design phase: (XPower Analyzer)

- System integration phase: (Lab measurements)

- Accurate power calculation at an early stage in the design cycle will result in fewer problems later

- The Power Estimator spreadsheet and the XPower Analyzer can be used for estimating the power consumption and the junction temperature of all Xilinx FPGA and CPLD devices

- The Power Estimator and XPower Analyzer uses activity rates to calculate total average power consumption

## Where Can I Learn More?

- Command Line Tools User Guide: XPower chapter

- $\mathsf{Help} \to \mathsf{Software}\ \mathsf{Manuals} \to \mathsf{Command}\ \mathsf{Line}\ \mathsf{Tools}\ \mathsf{User}\ \mathsf{Guide}$

- Online help from the XPower GUI

- Xilinx Power Solutions Web Page

- ▶ www.support.xilinx.com → Technology Solutions → Power Solutions

- Get the XPower Estimator spreadsheets for all Xilinx devices

- > 7 Steps to Worst Case Power Estimation, WP353

- Spartan-6 Power Management User Guide, UG394

- > Power Consumption at 40 and 45 nm, 298

- Application Notes: Help → Xilinx on the Web → Xilinx Application Notes

- Application Note XAPP158: *Powering Xilinx FPGAs*

#### **Xilinx Training**

- www.xilinx.com/training

- · Xilinx tools and architecture courses

- Hardware description language courses

- Basic FPGA architecture and other topics (free training videos)

### **Trademark Information**

Xilinx is disclosing this Document and Intellectual Propery (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2009 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.