Digital Design: An Embedded Systems Approach Using Verilog

#### Chapter 3 Numeric Basics

Portions of this work are from the book, *Digital Design: An Embedded Systems Approach Using Verilog,* by Peter J. Ashenden, published by Morgan Kaufmann Publishers, Copyright 2007 Elsevier Inc. All rights reserved.

#### **Numeric Basics**

- Representing and processing numeric data is a common requirement

- unsigned integers

- signed integers

- fixed-point real numbers

- floating-point real numbers

- complex numbers

# **Unsigned Integers**

- Non-negative numbers (including 0)

- Represent real-world data

- e.g., temperature, position, time, …

- Also used in controlling operation of a digital system

- e.g., counting iterations, table indices

- Coded using unsigned binary (base 2) representation

- analogous to decimal representation

# **Binary Representation**

- Decimal: base 10

124<sub>10</sub> = 1×10<sup>2</sup> + 2×10<sup>1</sup> + 4×10<sup>0</sup>

Binary: base 2

124<sub>10</sub> = 1×2<sup>6</sup>+1×2<sup>5</sup>+1×2<sup>4</sup>+1×2<sup>3</sup>+1×2<sup>2</sup>+0×2<sup>1</sup>+0×2<sup>0</sup> = 1111100<sub>2</sub>

- In general, a number x is represented using n bits as x<sub>n-1</sub>, x<sub>n-2</sub>, ..., x<sub>0</sub>, where

$$x = x_{n-1} 2^{n-1} + x_{n-2} 2^{n-2} + \dots + x_0 2^0$$

#### **Binary Representation**

Unsigned binary is a code for numbers

- *n* bits: represent numbers from 0 to  $2^n 1$

- 0: 0000...00; 2<sup>*n*</sup>− 1: 1111...11

- To represent x:  $0 \le x \le N 1$ , need  $\lceil \log_2 N \rceil$  bits

- Computers use

- 8-bit bytes: 0, ..., 255

- 32-bit words: 0, ..., ~4 billion

- (rather recently, 64-bit words)

- Digital circuits can use what ever size is appropriate

# **Unsigned Integers in Verilog**

Verilog

Use vectors as the representation

Can apply arithmetic operations

```

module multiplexer_6bit_4_to_1

( output reg [5:0] z,

input [5:0] a0, a1, a2, a3,

input [1:0] sel );

always @*

case (sel)

2'b00: z = a0;

2'b01: z = a1;

2'b11: z = a2;

2'b11: z = a3;

endcase

endmodule

```

#### **Octal and Hexadecimal**

- Short-hand notations for vectors of bits

- Octal (base 8)

- Each group of 3 bits represented by a digit

- 0: 000, 1:001, 2: 010, ..., 7: 111

- $253_8 = 010\ 101\ 011_2$

- $11001011_2 \Rightarrow 11\ 001\ 011_2 = 313_8$

- Hex (base 16)

- Each group of 4 bits represented by a digit

- 0: 0000, ..., 9: 1001, A: 1010, ..., F: 1111

- $3CE_{16} = 0011 \ 1100 \ 1110_2$

- $11001011_2 \Rightarrow 1100 \ 1011_2 = CB_{16}$

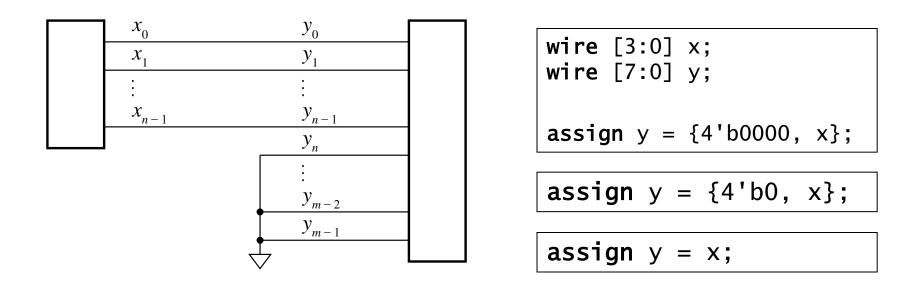

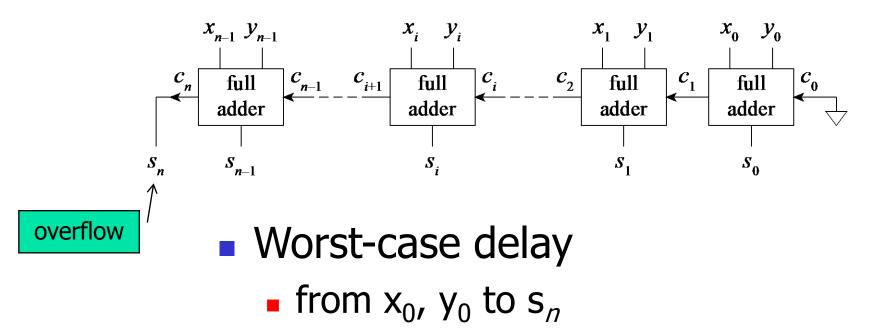

# **Extending Unsigned Numbers**

Verilog

To extend an *n*-bit number to *m* bits

Add leading 0 bits

e.g., 72<sub>10</sub> = 1001000 = 000001001000

# **Truncating Unsigned Numbers**

- To truncate from *m* bits to *n* bits

- Discard leftmost bits

- Value is preserved if discarded bits are 0

- Result is x mod 2<sup>n</sup>

assign

$$x = y[3:0];$$

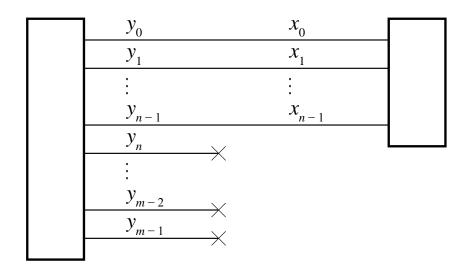

# **Unsigned Addition**

Verilog

Performed in the same way as decimal

# **Addition Circuits**

#### Half adder

for least-significant bits

$s_0 = x_0 \oplus y_0$

$$c_1 = x_0 \cdot y_0$$

- Full adder

- for remaining bits  $s_i = (x_i \oplus y_i) \oplus c_i$

| $C_{i+1}$  | $= X_i$ | $\cdot y_i$       | $+(x_i)$ | $\oplus y_i$                | $) \cdot C_i$ |

|------------|---------|-------------------|----------|-----------------------------|---------------|

| $\iota$ +1 | l       | $\mathcal{I}_{l}$ |          | $\mathcal{I}_{\mathcal{I}}$ |               |

| x <sub>i</sub> | y <sub>i</sub> | C <sub>i</sub> | s <sub>i</sub> | <i>C</i> <sub><i>i</i>+1</sub> |

|----------------|----------------|----------------|----------------|--------------------------------|

| 0              | 0              | 0              | 0              | 0                              |

| 0              | 0              | 1              | 1              | 0                              |

| 0              | 1              | 0              | 1              | 0                              |

| 0              | 1              | 1              | 0              | 1                              |

| 1              | 0              | 0              | 1              | 0                              |

| 1              | 0              | 1              | 0              | 1                              |

| 1              | 1              | 0              | 0              | 1                              |

| 1              | 1              | 1              | 1              | 1                              |

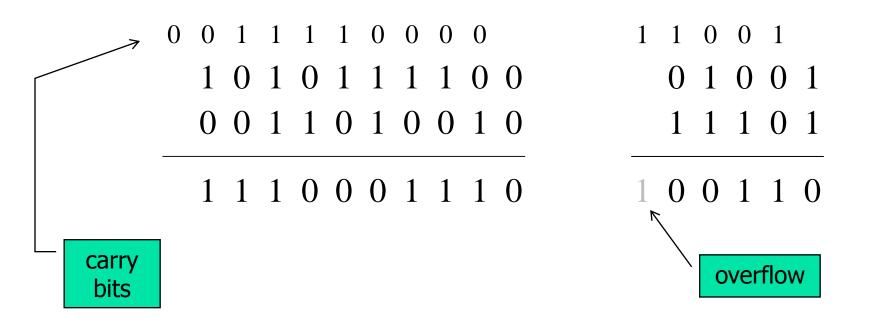

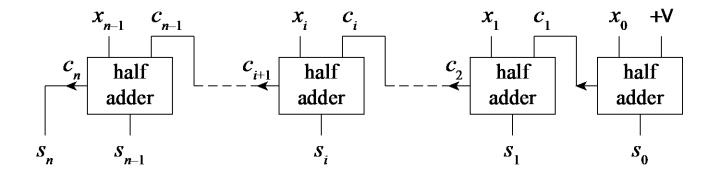

#### **Ripple-Carry Adder**

• Full adder for each bit,  $c_0 = 0$

carry must ripple through intervening stages, affecting sum bits

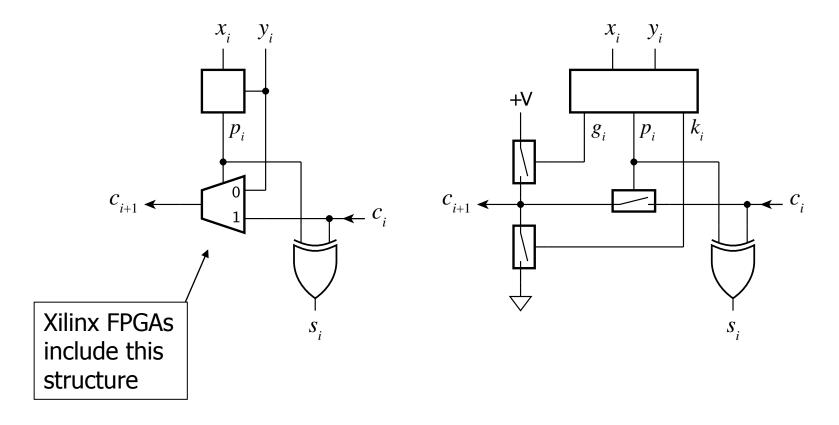

#### Verilog **Improving Adder Performance** $C_i$ $k_i = x_i \cdot y_i$ $X_i$ $y_i$ $S_i$ $C_{i+1}$ Carry kill: $\mathbf{0}$ Carry propagate: $p_i = x_i \oplus y_i$ $\mathbf{0}$ Carry generate: $g_i = x_i \cdot y_i$

Adder equations

$$s_i = p_i \oplus c_i$$

$c_{i+1} = g_i + p_i \cdot c_i$

Digital Design — Chapter 3 — Numeric Basics

#### Fast-Carry-Chain Adder

#### Also called Manchester adder

$$c_{i+1} = g_i + p_i \cdot c_i$$

$$c_{1} = g_{0} + p_{0} \cdot c_{0}$$

$$c_{2} = g_{1} + p_{1} \cdot (g_{0} + p_{0} \cdot c_{0}) = g_{1} + p_{1} \cdot g_{0} + p_{1} \cdot p_{0} \cdot c_{0}$$

$$c_{3} = g_{2} + p_{2} \cdot g_{1} + p_{2} \cdot p_{1} \cdot g_{0} + p_{2} \cdot p_{1} \cdot p_{0} \cdot c_{0}$$

$$c_{4} = g_{3} + p_{3} \cdot g_{2} + p_{3} \cdot p_{2} \cdot g_{1}$$

$$+ p_{3} \cdot p_{2} \cdot p_{1} \cdot g_{0} + p_{3} \cdot p_{2} \cdot p_{1} \cdot p_{0} \cdot c_{0}$$

Digital Design — Chapter 3 — Numeric Basics

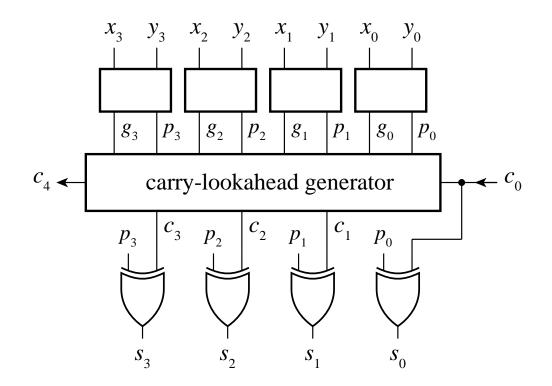

#### Carry-Lookahead Adder

Verilog

Avoids chained carry circuit

Use multilevel lookahead for wider numbers

Digital Design — Chapter 3 — Numeric Basics

# **Other Optimized Adders**

- Other adders are based on other reformulations of adder equations

- Choice of adder depends on constraints

- e.g., ripple-carry has low area, so is ok for low performance circuits

- e.g., Manchester adder ok in FPGAs that include carry-chain circuits

## Adders in Verilog

#### Use arithmetic "+" operator

wire [7:0] a, b, s; ...

assign s = a + b;

```

wire [8:0] tmp_result;

wire c;

...

assign tmp_result = {1'b0, a} + {1'b0, b};

assign c = tmp_result[8];

assign s = tmp_result[7:0];

assign {c, s} = {1'b0, a} + {1'b0, b};

assign {c, s} = a + b;

```

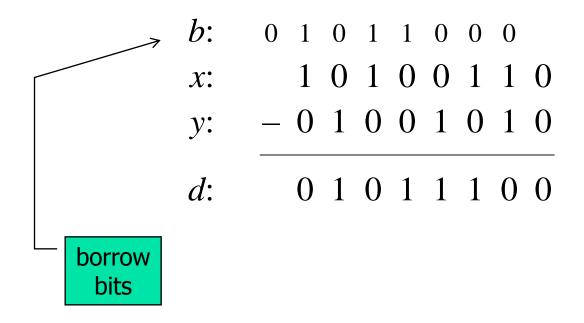

#### **Unsigned Subtraction**

#### As in decimal

#### **Subtraction Circuits**

#### For least-significant bits

$$d_0 = x_0 \oplus y_0$$

$$b_1 = \overline{x_0} \cdot y_0$$

Verilog

For remaining bits

$$d_i = (x_i \oplus y_i) \oplus b_i$$

$$b_{i+1} = \overline{x_i} \cdot y_i + \overline{(x_i \oplus y_i)} \cdot b_i$$

| X <sub>i</sub> | y <sub>i</sub> | $b_i$ | s <sub>i</sub> | $b_{i+1}$ |

|----------------|----------------|-------|----------------|-----------|

| 0              | 0              | 0     | 0              | 0         |

| 0              | 0              | 1     | 1              | 1         |

| 0              | 1              | 0     | 1              | 1         |

| 0              | 1              | 1     | 0              | 1         |

| 1              | 0              | 0     | 1              | 0         |

| 1              | 0              | 1     | 0              | 0         |

| 1              | 1              | 0     | 0              | 0         |

| 1              | 1              | 1     | 1              | 1         |

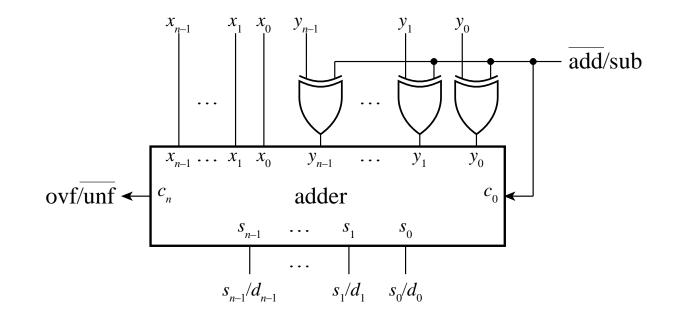

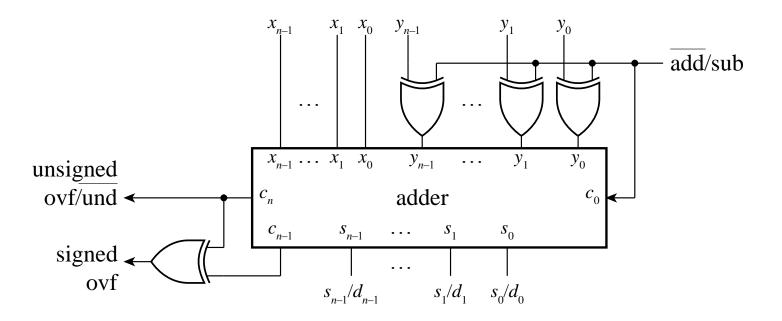

#### Adder/Subtracter Circuits

- Many systems add and subtract

- Trick: use complemented borrows

- HW: use boolean algebra to derive equations on the right from equations on the previous page

# AdditionSubtraction $s_i = (x_i \oplus y_i) \oplus c_i$ $d_i = (x_i \oplus \overline{y_i}) \oplus \overline{b_i}$ $c_{i+1} = x_i \cdot y_i + (x_i \oplus y_i) \cdot c_i$ $\overline{b_{i+1}} = x_i \cdot \overline{y_i} + (x_i \oplus \overline{y_i}) \cdot \overline{b_i}$

Same hardware can perform both

For subtraction: complement y, set b<sub>0</sub> = 1

# Adder/Subtracter Circuits

Verilog

Adder can be any of those we have seen

depends on constraints

### Subtraction in Verilog

#### **Increment and Decrement**

• Adding 1: set y = 0 and  $c_0 = 1$

Verilog

$s_i = x_i \oplus c_i$   $c_{i+1} = x_i \cdot c_i$

These are equations for a half adder

Similarly for decrementing: subtracting 1

Digital Design — Chapter 3 — Numeric Basics

#### **Increment/Decrement in Verilog**

Just add or subtract 1

Verilog

wire [15:0] x, s; ... assign s = x + 1; // increment x assign s = x - 1; // decrement x

- Note: 1 (integer), not 1'b1 (bit)

- Automatically resized

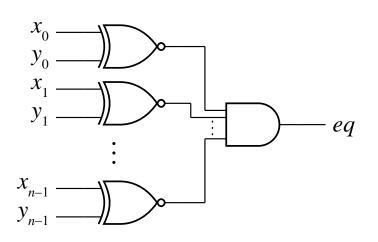

# **Equality Comparison**

# XNOR gate: equality of two bits Apply bitwise to two unsigned numbers

- In Verilog, x == y gives a bit result

- 1'b0 for false, 1'b1 for true

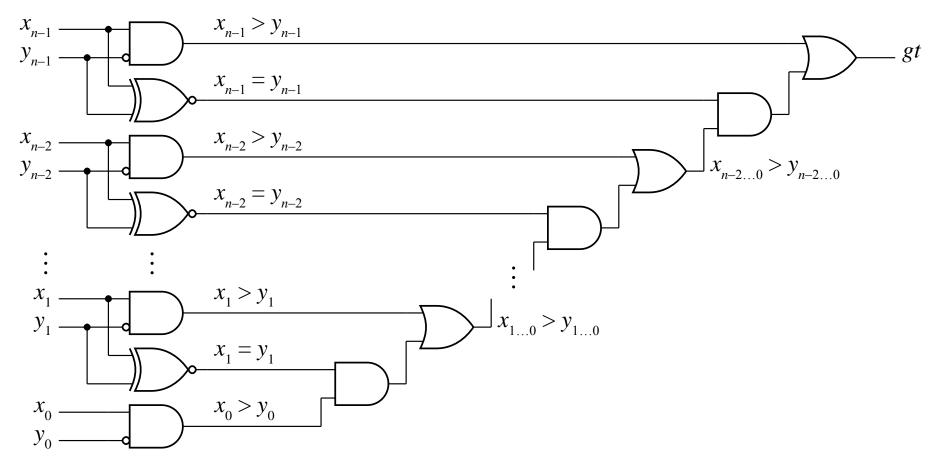

### **Inequality Comparison**

Verilog

Magnitude comparator for x > y

Digital Design — Chapter 3 — Numeric Basics

#### **Comparison Example in Verilog**

Verilog

Thermostat with target termperature

Heater or cooler on when actual temperature is more than 5° from target

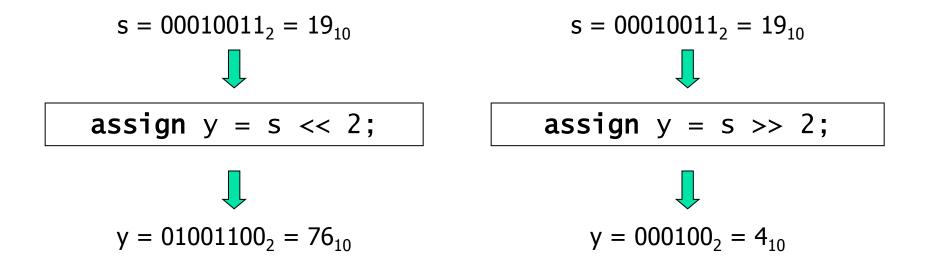

### Scaling by Power of 2

$$x = x_{n-1} 2^{n-1} + x_{n-2} 2^{n-2} + \dots + x_0 2^0$$

$2^{k} x = x_{n-1} 2^{k+n-1} + x_{n-2} 2^{k+n-2} + \dots + x_0 2^{k} + (0) 2^{k-1} + \dots + (0) 2^{0}$

- This is x shifted left k places, with k bits of 0 added on the right

- Iogical shift left by k places

- e.g.,  $00010110_2 \times 2^3 = 00010110000_2$

- Truncate if result must fit in *n* bits

overflow if any truncated bit is not 0

#### Scaling by Power of 2

$$x = x_{n-1}2^{n-1} + x_{n-2}2^{n-2} + \dots + x_02^0$$

$x/2^{k} = x_{n-1}2^{n-1-k} + x_{n-2}2^{n-2-k} + \dots + x_{k}2^{0} + x_{k-1}2^{-1} + \dots + x_{0}2^{-k}$

- This is x shifted right k places, with k bits truncated on the right

- Iogical shift right by k places

- e.g., 01110110<sub>2</sub> / 2<sup>3</sup> = 01110<sub>2</sub>

- Fill on the left with k bits of 0 if result must fit in n bits

# Scaling in Verilog

Verilog

Shift-left (<<) and shift-right (>>) operations

result is same size as operand

#### **Unsigned Multiplication**

$$xy = x \left( y_{n-1} 2^{n-1} + y_{n-2} 2^{n-2} + \dots + y_0 2^0 \right)$$

$$= y_{n-1} x 2^{n-1} + y_{n-2} x 2^{n-2} + \dots + y_0 x 2^0$$

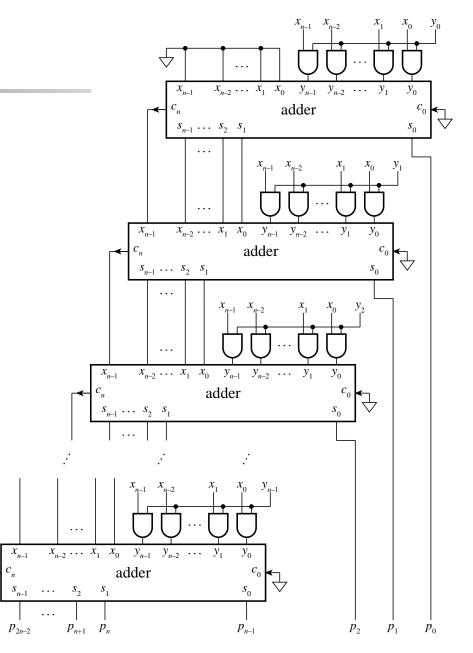

# y<sub>i</sub>x 2<sup>i</sup> is called a partial product if y<sub>i</sub> = 0, then y<sub>i</sub>x 2<sup>i</sup> = 0 if y<sub>i</sub> = 1, then y<sub>i</sub>x 2<sup>i</sup> is x shifted left by i Combinational array multiplier AND gates form partial products adders form full product

#### Unsigned Multiplication

- Adders can be any of those we have seen

- Optimized multipliers combine parts of adjacent adders

Digital Design — Chapter 3 — Numeric Basics

$p_{2n-1}$

#### **Product Size**

Greatest result for *n*-bit operands:

$(2^{n}-1)(2^{n}-1) = 2^{2n}-2^{n}-2^{n}+1 = 2^{2n}-(2^{n+1}-1)$

- Requires 2n bits to avoid overflow

- Multiplying *n*-bit and *m*-bit operands

requires *n* + *m* bits

wire [ 7:0] x; wire [13:0] y; wire [21:0] p;

...

assign p = {14'b0, x} \* {8'b0, y};

assign p = x \* y; // implicit resizing

Digital Design — Chapter 3 — Numeric Basics

# **Other Unsigned Operations**

Division, remainder

- More complicated than multiplication

- Large circuit area, power

- Complicated operations are often performed sequentially

- in a sequence of steps, one per clock cycle

- cost/performance/power trade-off

# Signed Integers

- Positive and negative numbers (and 0)

- *n*-bit *signed magnitude* code

- 1 bit for sign: 0  $\Rightarrow$  +, 1  $\Rightarrow$  -

- *n* − 1 bits for magnitude

- Signed-magnitude rarely used for integers now

- circuits are too complex

- Use 2s-complement binary code

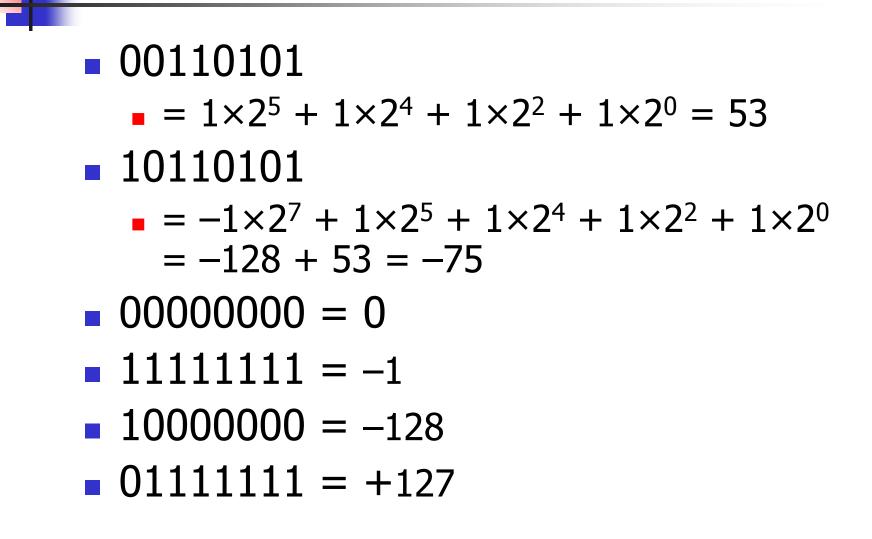

### **2s-Complement Representation**

$$x = -x_{n-1}2^{n-1} + x_{n-2}2^{n-2} + \dots + x_02^0$$

Most-negative number

$$\bullet 1000...0 = -2^{n-2}$$

Verilog

Most-positive number

$$0111...1 = +2^{n-1} - 1$$

•  $x_{n-1} = 1 \Rightarrow negative,$   $x_{n-1} = 0 \Rightarrow non-negative$ • Since  $2^{n-2} + \dots + 2^0 = 2^{n-1} - 1$

### **2s-Complement Examples**

```

Verilog

```

# Signed Integers in Verilog

Use signed vectors

wire signed [ 7:0] a; reg signed [13:0] b;

### Can convert between signed and unsigned interpretations

assign s1= \$unsigned(s2); // s2 is known to be nonnegative

## Octal and Hex Signed Integers

- Don't think of signed octal or hex

- Just treat octal or hex as shorthand for a vector of bits

- E.g.,  $844_{10}$  is 001101001100• In hex: 0011 0100 1100  $\Rightarrow$  34C

- E.g., -42<sub>10</sub> is 1111010110

Verilog

• In octal: 1 111 010 110  $\Rightarrow$  1726 (10 bits)

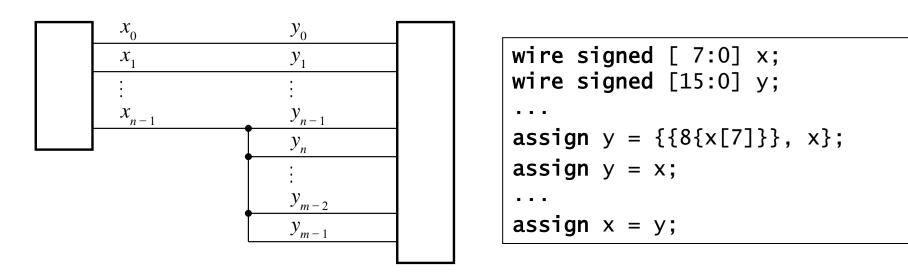

### **Resizing Signed Integers**

- To extend a non-negative number

- Add leading 0 bits

- e.g., 53<sub>10</sub> = 00110101 = 000000110101

- To truncate a non-negative number

- Discard leftmost bits, provided

- discarded bits are all 0

- sign bit of result is 0

- E.g., 41<sub>10</sub> is 00101001

- Truncating to 6 bits: 101001 error!

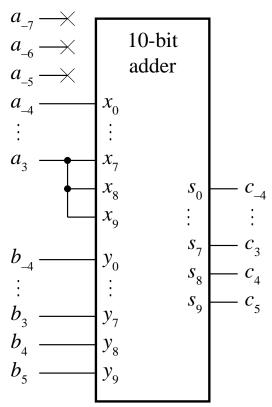

# **Resizing Signed Integers**

To extend a negative number

Add leading 1 bits

See textbook for proof

e.g., -75<sub>10</sub> = 10110101 = 111110110101

To truncate a negative number

Discard leftmost bits, provided

discarded bits are all 1

sign bit of result is 1

### **Resizing Signed Integers**

- In general, for 2s-complement integers

- Extend by replicating sign bit

- sign extension

Verilog

- Truncate by discarding leading bits

- Discarded bits must all be the same, and the same as the sign bit of the result

Digital Design — Chapter 3 — Numeric Basics

### Signed Negation

- Complement and add 1 • Note that  $x_i = 1 - x_i$  $x+1 = -(1-x_{n-1})2^{n-1} + (1-x_{n-2})2^{n-2} + \dots + (1-x_n)2^0 + 1$  $= -2^{n-1} + x_{n-1}2^{n-1} + 2^{n-2} - x_{n-2}2^{n-2} + \dots + 2^0 - x_02^0 + 1$  $= -(-x_{n-1}2^{n-1} + x_{n-2}2^{n-2} + \dots + x_02^0)$  $-2^{n-1}+(2^{n-2}+\cdots+2^{0})+1$  $=-x-2^{n-1}+2^{n-1}=-x$ E.g., 43 is 00101011

- so -43 is 11010100 + 1 = 11010101

Digital Design — Chapter 3 — Numeric Basics

### Signed Negation

- What about negating −2<sup>*n*−1</sup>?

- $1000...00 \Rightarrow 0111...11 + 1 = 1000...00$

- Result is  $-2^{n-1}!$

- Recall range of *n*-bit numbers is not symmetric

- Either check for overflow, extend by one bit, or ensure this case can't arise

- In Verilog: use operator

- E.g., assign y = -x;

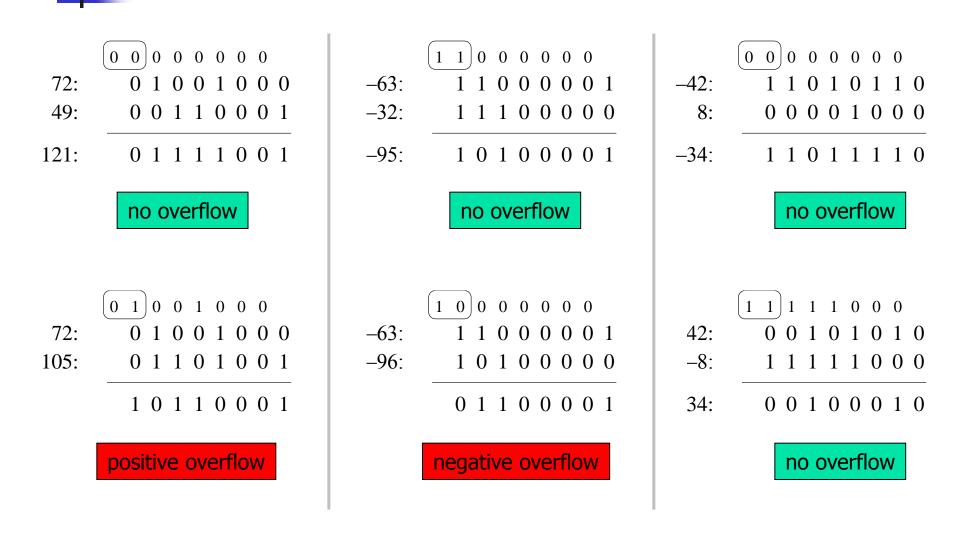

### Signed Addition

$$x = -x_{n-1}2^{n-1} + x_{n-2...0} \qquad y = -y_{n-1}2^{n-1} + y_{n-2...0}$$

$$x + y = -(x_{n-1} + y_{n-1})2^{n-1} + x_{n-2...0} + y_{n-2...0}$$

$$\underbrace{yields \ c_{n-1}}$$

- Perform addition as for unsigned

Overflow if c<sub>n-1</sub> differs from c<sub>n</sub>

See textbook for case analysis

- Can use the same circuit for signed and unsigned addition

### Signed Addition Examples

# Signed Addition in Verilog

### Result of + is same size as operands

```

wire signed [11:0] v1, v2;

wire signed [12:0] sum;

...

assign sum = {v1[11], v1} + {v2[11], v2};

...

assign sum = v1 + v2; // implicit sign extension

```

### To check overflow, compare signs

```

wire signed [7:0] x, y, z;

wire ovf;

...

assign z = x + y;

assign ovf = ~x[7] & ~y[7] & z[7] | x[7] & y[7] & ~z[7];

```

Digital Design — Chapter 3 — Numeric Basics

### Signed Subtraction

$$x - y = x + (-y) = x + y + 1$$

# Use a 2s-complement adder Complement y and set c<sub>0</sub> = 1

Digital Design — Chapter 3 — Numeric Basics

### **Other Signed Operations**

- Increment, decrement

- same as unsigned

- Comparison

- =, same as unsigned

- >, compare sign bits using  $\overline{x_{n-1}} \cdot y_{n-1}$

- Multiplication

- Complicated by the need to sign extend partial products

- Refer to Further Reading

### Scaling Signed Integers

Multiplying by 2<sup>k</sup>

- logical left shift (as for unsigned)

- truncate result using 2s-complement rules

- Dividing by 2<sup>k</sup>

- arithmetic right shift

- discard k bits from the right, and replicate sign bit k times on the left

- e.g., s = "11110011" -- -13 shift\_right(s, 2) = "11111100" -- -13 / 2<sup>2</sup>

### **Fixed-Point Numbers**

- Many applications use non-integers

especially signal-processing apps

- Fixed-point numbers

- allow for fractional parts

- represented as integers that are implicitly scaled by a power of 2

- can be unsigned or signed

### **Positional Notation**

### In decimal

$10.24_{10} = 1 \times 10^{1} + 0 \times 10^{0} + 2 \times 10^{-1} + 4 \times 10^{-2}$

### In binary

$101.01_2 = 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 0 \times 2^{-1} + 1 \times 2^{-2} = 5.25_{10}$

# Represent as a bit vector: 10101 binary point is implicit

### **Unsigned Fixed-Point**

*n*-bit unsigned fixed-point

*m* bits before and *f* bits after binary point

$$x = x_{m-1} 2^{m-1} + \dots + x_0 2^0 + x_{-1} 2^{-1} + \dots + x_{-f} 2^{-f}$$

- Range: 0 to 2<sup>*m*</sup> − 2<sup>−*f*</sup>

- Precision: 2<sup>-f</sup>

Verilog

*m* may be ≤ 0, giving fractions only

e.g., *m*= −2: 0.0001001101

# Signed Fixed-Point

*n*-bit signed 2s-complement fixed-point

*m* bits before and *f* bits after binary point

$$x = -x_{m-1}2^{m-1} + \dots + x_02^0 + x_{-1}2^{-1} + \dots + x_{-f}2^{-f}$$

- Range:  $-2^{m-1}$  to  $2^{m-1} 2^{-f}$

- Precision: 2<sup>-f</sup>

Verilog

• E.g., 111101, signed fixed-point, m = 2• 11.1101<sub>2</sub> = -2 + 1 + 0.5 + 0.25 + 0.0625=  $-0.1875_{10}$

# **Choosing Range and Precision**

- Choice depends on application

- Need to understand the numerical behavior of computations performed

- some operations can magnify quantization errors

- In DSP

Verilog

- fixed-point range affects dynamic range

- precision affects signal-to-noise ratio

Perform simulations to evaluate effects

# Fixed-Point in Verilog

Verilog

Use vectors with implied scaling

- Index range matches powers of weights

- Assume binary point between indices 0 and -1

### **Fixed-Point Operations**

Verilog

Just use integer hardware e.g., addition:  $x + y = (x \times 2^{f} + y \times 2^{f})/2^{f}$ Ensure binary points are aligned

### Summary

- Unsigned:  $x = x_{n-1}2^{n-1} + x_{n-2}2^{n-2} + \dots + x_02^0$

- Signed:  $x = -x_{n-1}2^{n-1} + x_{n-2}2^{n-2} + \dots + x_02^0$

- Octal and Hex short-hand

- Operations: resize, arithmetic, compare

- Arithmetic circuits trade off speed/area/power

- Fixed- and floating-point non-integers

- Gray codes for position encoding