# Lab 1: Tools tutorial CMPE 415 UMBC

February 1st, 2012 Due February 8th 2012 (at 2:30 pm)

# 1 Objective

The objective of this lab is to learn the fundamental components of the Xilinx FGPA tools required to enter and assemble HDL code using a schematic entry tool and program an FPGA. This includes integrating HDL into a schematic, as well as creating and updating symbols.

# 2 Intro

In this lab you will program an FPGA to display a rectangle on a monitor using a VGA cable. You will \_rst create an implementation with an error in it and view the results. You will then modify the code, update the symbol in the schematic, and wire the schematic correctly to control the color of the rectangle using switches.

# 3 Tutorial Steps

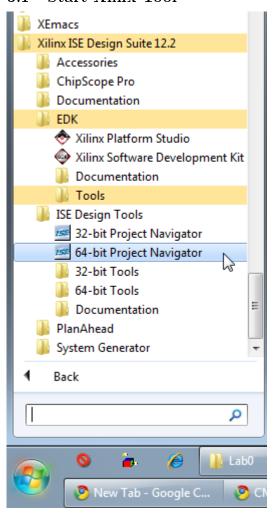

# 3.1 Start Xlinx Tool

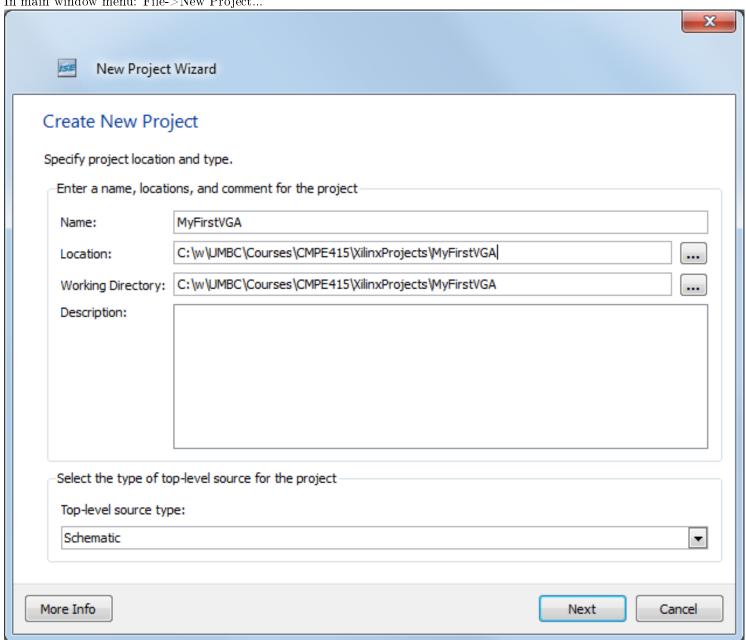

## Create New Project

1. In main window menu: File->New Project...

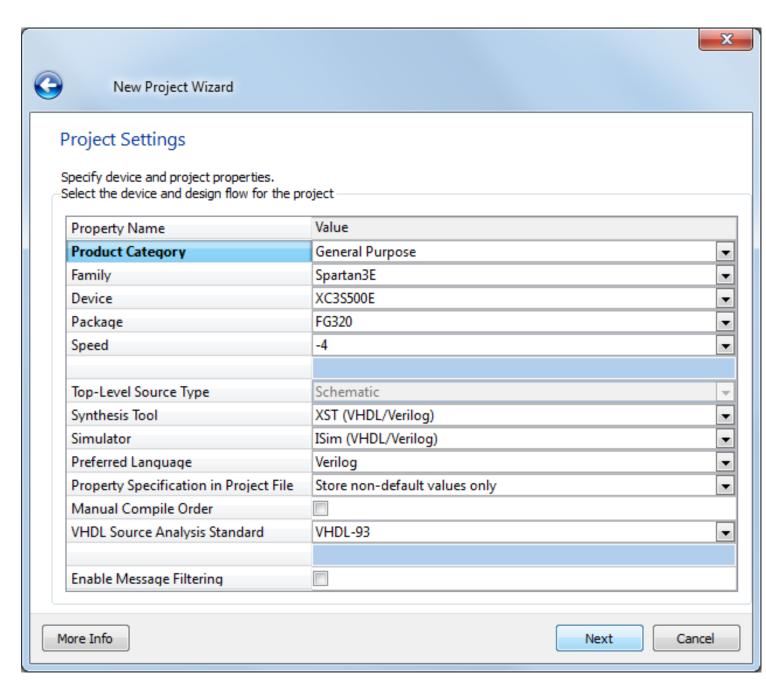

2. You'll now need to enter information about the FPGA. You can look in "Spartan-3E FPGA Family: Data Sheet" under Package Marking (page 6). To find this information. http://www.xilinx.com/support/documentation/data\_sheets/ds312.pdf

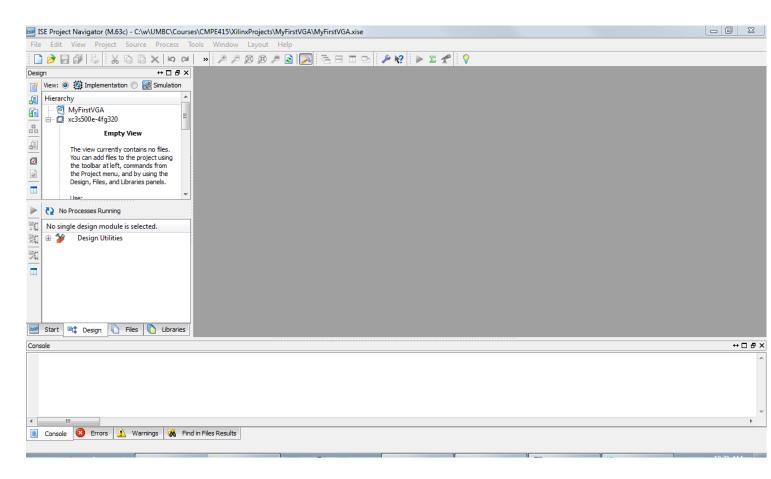

3. The next screen shows a summay. Hit Finish. Result:

## 3.3 Downloaded HDL Module and Add to project

- 1. Download a free HDL description of implementation of a vga module to a temporary directory or to your project directory. Our other module will be implemented using Verilog, but we can integrate Verilog and VHDL modules together in the schematic if desired. Here are examples of the type of vga modules for which you are looking. Make sure to respect any restrictions the authors place on copywrighted code that you use.

- $\verb| http://web.mit.edu/6.111/www/f2005/code/jtag2mem\_6111/vga\_sync.v \ Verilog \ implementation \ (Is uggest \ this \ one.)$

- $\bullet \ http://www.ece.gatech.edu/academic/courses/fpga/Xilinx/downloads/vga\_sync.vhd\ VHDL\ implementation\ (handles\ blanking\ internally)$

- $\bullet \ http://jjackson.eng.ua.edu/courses/ece 480/assignments/vga\_sync.vhd\ VHDL\ implementation\ with\ parameters\ to\ set\ various\ resolutions\ (also,\ implements\ a\ "video\_on"\ signal\ instead\ of\ a\ "blank"\ signal\ )$

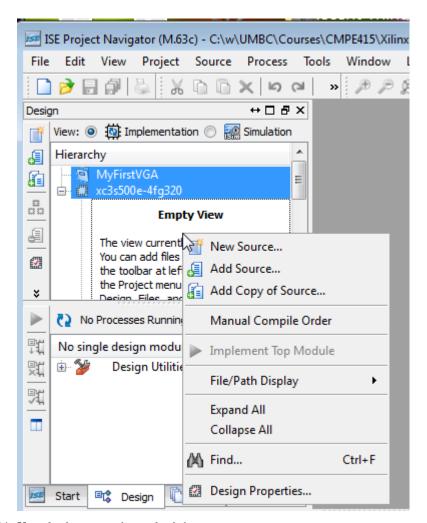

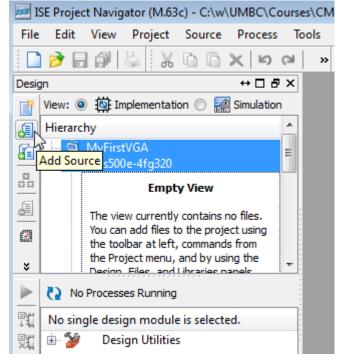

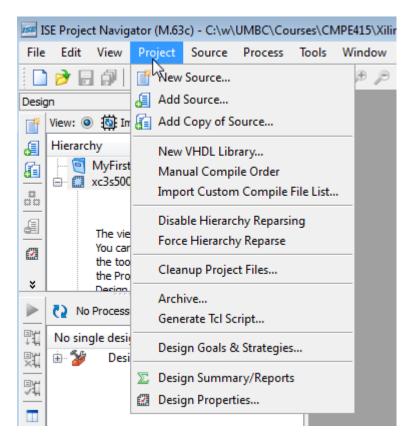

- 2. There are three places to access the project functions, such as adding a source. You can use any of the following (a,b,c):

- (a) Right-click in the Hierarchy plane

(b) Use the buttons along the left.

(c) Use the main window Project menu

#### 3. The three functions for sources are:

- (a) New Source starts wizard to create a new source file (Verilog, VHDL, Schematic, etc...), creating a shell if desired, and adds it for use in the project.

- (b) Add Source Allows you to point to a source file in the project directory or anywhere else and include it for use in the project

- (c) Add Copy of Source Creates a copy of the source file in the project directory and adds the copy for use in the project

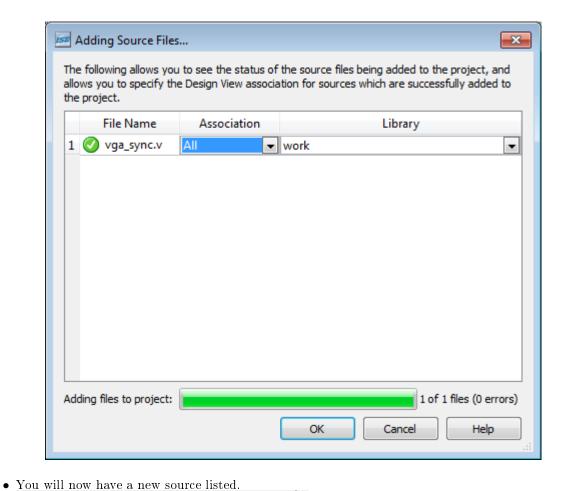

- Add the downloaded HDL file using option (b) "Add Source" if you initially downloaded the file to project directory and use option (c) "Add Copy of Source" if you downloaded it to a temporary directory.

# 3.4 Creating a Symbol

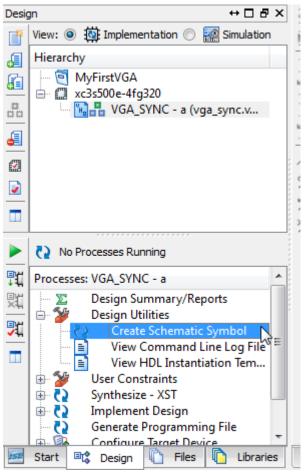

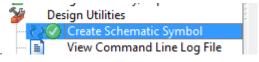

1. Select the new HDL source in the Hierarchy panel. In the lower panel expand Design Utilities and double-click "Create Schematic Symbol".

If needed, see help of: Creating a Schematic Symbol from a Source File Help->Help Topics

$2. \ \,$  Notice the green check mark added upon success.

## 3.5 Create Top Schematic

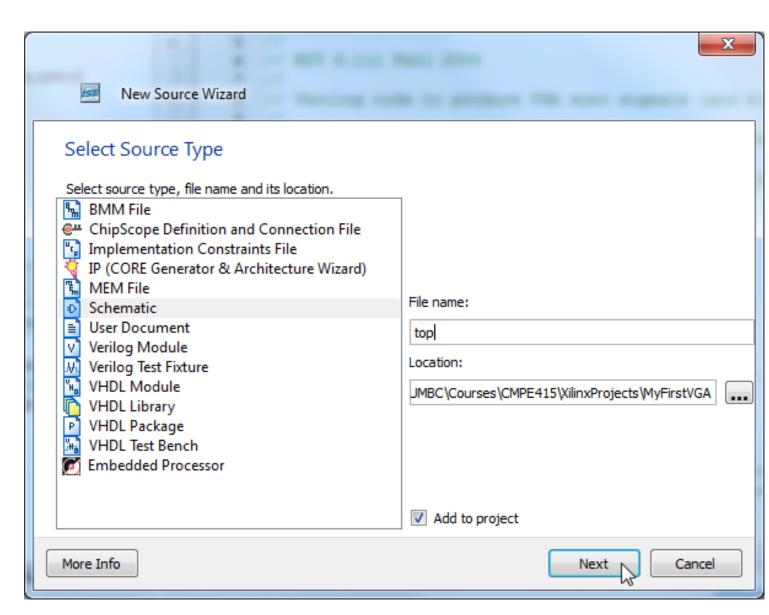

- 1. Using the main window Project menu, the buttons along the left, or a right-click in the Hierarchy view create a new source.

- 2. Project->New Source...

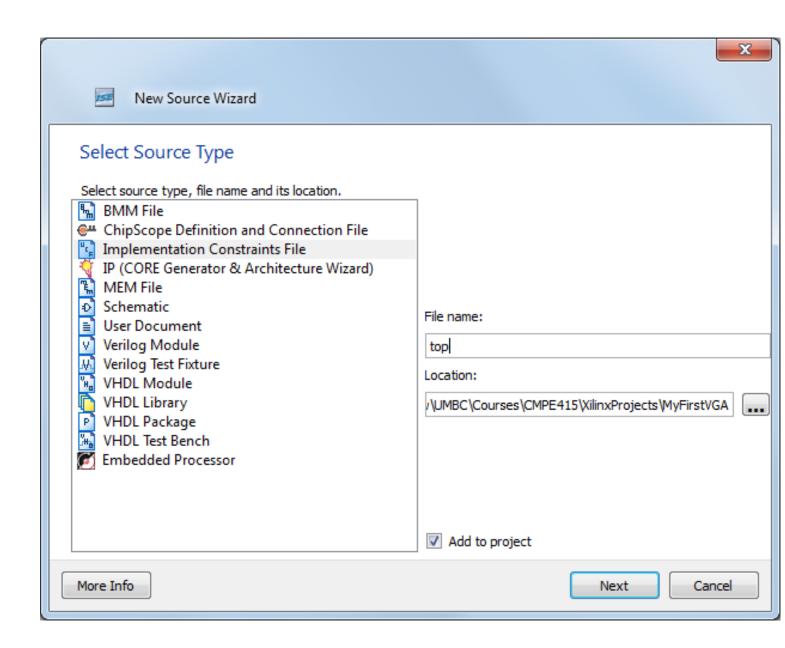

- 3. The New Source Wizard opens

- 4. Select Schematic as the type and top as the File Name. Click Next.

5. Click Finish in the following window.

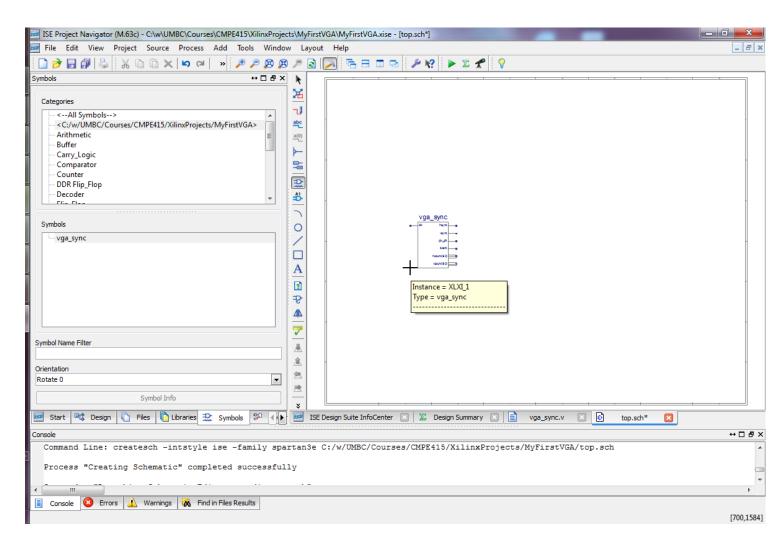

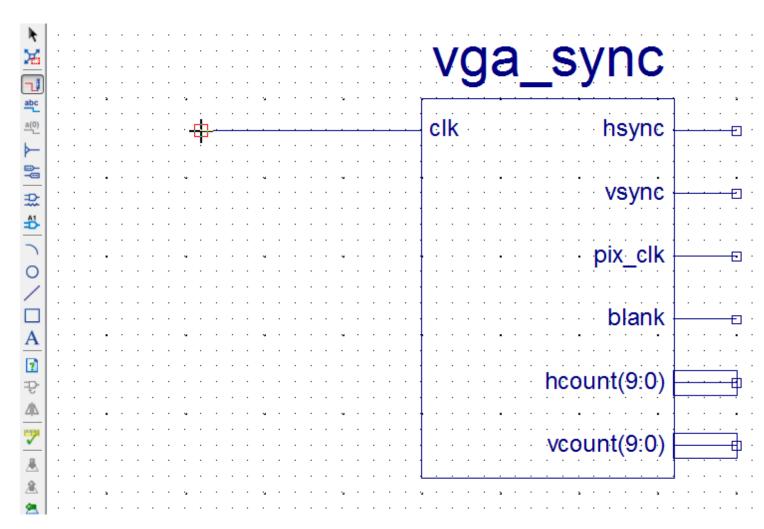

#### 3.6 Add Symbol

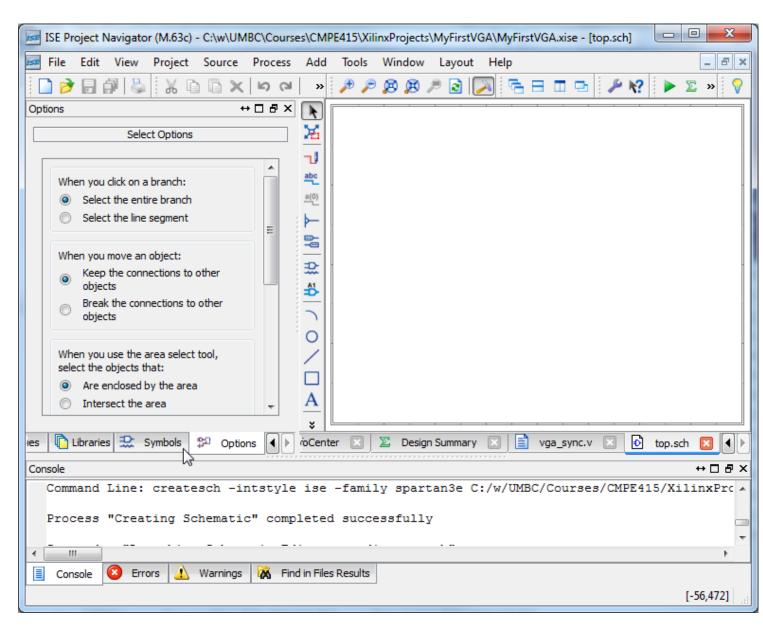

1. With your fresh sechmaic showing, select the Symbols tab as pointed out by the cursor in the picture. (use the scroll buttons just to the right if not shown)

- 2. Under Catagories, select your current project.

- 3. Under symbols, select your new symbol

- 4. Click in the schematic to add the symbol.

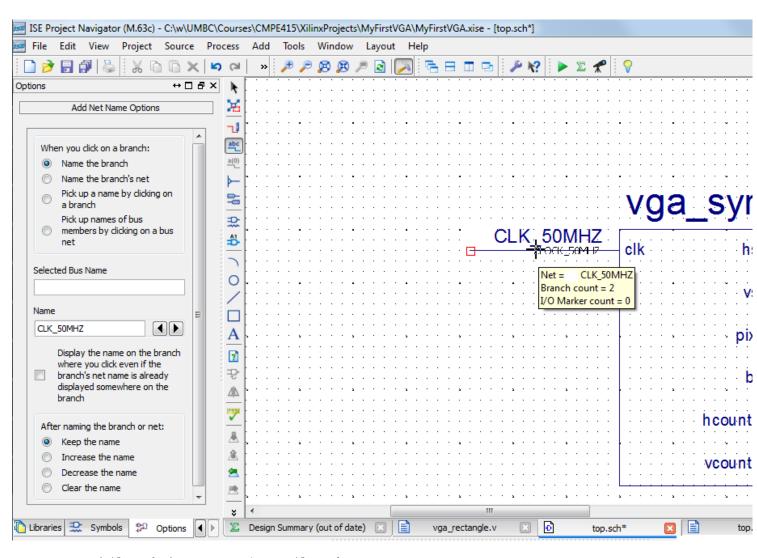

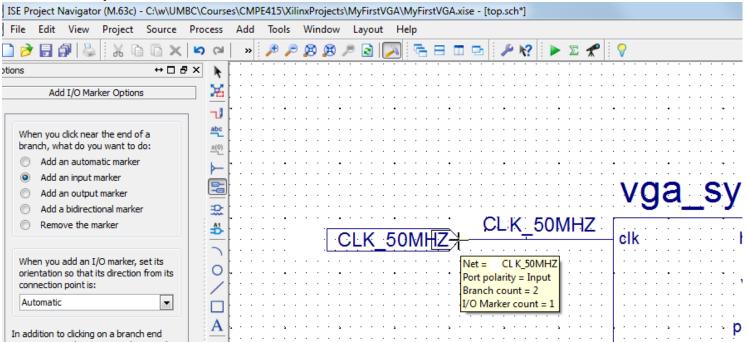

## 3.7 Add wire, name it, and and pin

- 1. Using Add menu or other documented means, choose Add->Wire

- 2. Click twice to add a simple wire as shown.

- 3. Add->Net Name

- 4. Type Name CLK\_50MHZ, and click on wire

- 5. Next, add pin (I/O Marker): Use Menu Add->I/O Marker

- 6. Select "Add an input marker" on left and click on end of wire.

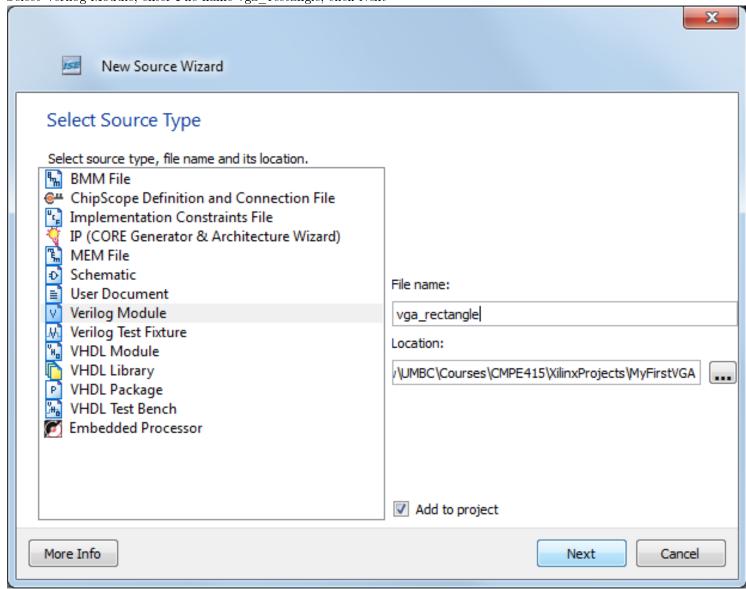

- 3.8 Add New Source for rectangle display driver using Source Wizard

- 1. Main window menu: Project->New Source

2. Select Verilog Module, enter File name vga rectangle, click Next

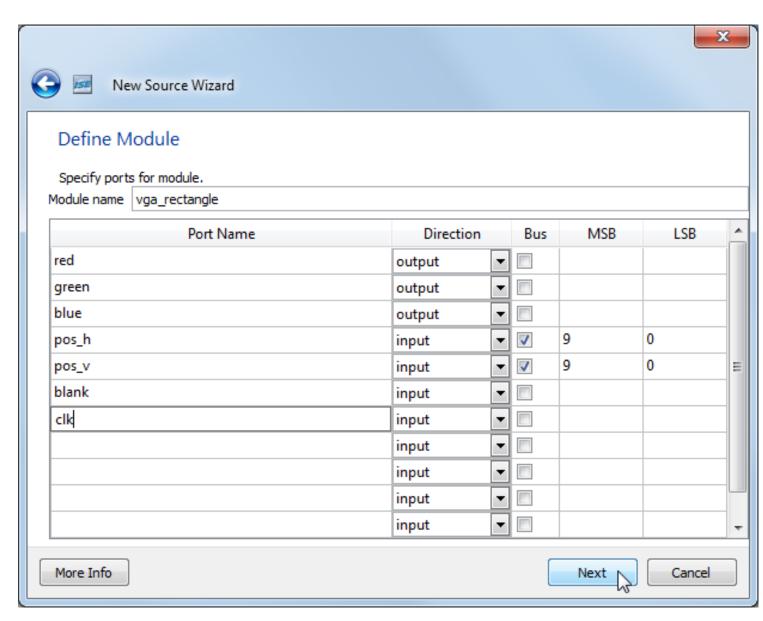

3. Set up the IO as shown and then click Next and then click Finish in the following window.

4. You should now have a shell created with port definitions. Set the reg, green, and blue outputs as registers. Implementing registers avoids glitching (not that it is critical here). change

```

output red,

output green,

output blue,

to

output reg red,

output reg green,

output reg blue,

```

5. Add the following module code:

```

parameter WIDTH

20;

parameter HEGHT

100:

parameter X LEFT

= 320:

parameter Y BOTTOM = 240;

//addinal intermediate logic signal wires

//high only when over rectangle

wire flag on rect;

wire [9:0] x, y;

//traditional cartesean coordinates, (left, bottom)=(0,0)

//combinatorial logic to calculate x,y coordinate system

assign x = pos h;

assign y = 480 - pos v;

//combinatorial logic to decide if beam is over a rectange

assign flag on rect = x >= (X LEFT)

&&

(X LEFT + WIDTH)

&&

y >= (Y BOTTOM)

&&

y < (Y BOTTOM + HIEGHT);

//combinatorial logic and registers that load on rising clock edge

always @(posedge clk) begin

<= flag_on_rect & ~blank;</pre>

green <= ~flag on rect & ~blank;</pre>

flag on rect & ~blank;

blue

end

```

6. Save the file and generate a symbol as before

# 3.9 Complete Top Schematic

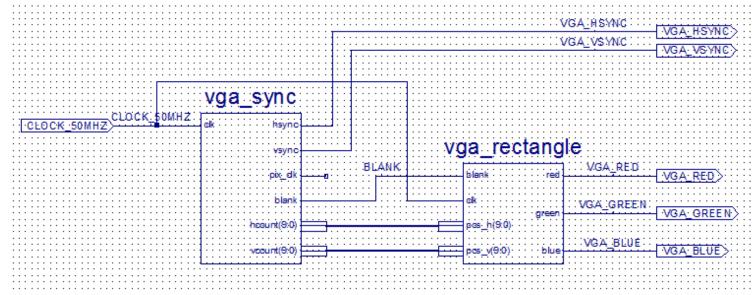

1. Complete the schematic as follows, including the output markers (be sure to make them as output markers, not input markers)

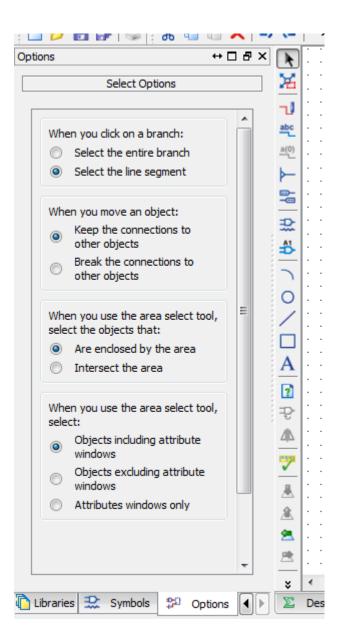

• Note the IMPORTANT OPTIONS for the Select(Arrow) tool. Thouroghly understand the first three options, reading the documentation as nessisary. Understanding these options could save you a lot of time.

## 3.10 Define Pin Locations

1. We need to add a user contrainst file. Use the new source wizard or create one called top: Project->New Source...

2. Click Next then Finish.

Page 57 of the developement board user guide provides pin locations for the vga port: http://www.digilentinc.com/Data/Pro Appendix B provides an Example User Constraints File (UCF) for the starter board, starting on page 159.

3. Copy the following lines to your UCF:

```

\# = Clock inputs (CLK) =

NET "CLK 50MHZ" LOC = "C9" | IOSTANDARD = LVCMOS33 ;

Define clock period for 50 MHz oscillator (40%/60% duty-cycle)

NET "CLK 50MHZ" PERIOD = 20.0 \,\mathrm{ns} HIGH 40\%;

\# = VGA Port (VGA) =

NET "VGA BLUE"

LOC = "G15"

IOSTANDARD = LVTTL

DRIVE = 8

SLEW = FAST;

NET "VGA GREEN"

LOC = "H15"

IOSTANDARD = LVTTL

DRIVE = 8

SLEW = FAST

LOC = "F15"

NET "VGA HSYNC"

IOSTANDARD = LVTTL

DRIVE = 8

SLEW = FAST

NET "VGA RED"

LOC = "H14"

IOSTANDARD = LVTTL

DRIVE = 8

SLEW = FAST

NET "VGA VSYNC" LOC = "F14" \mid

IOSTANDARD = LVTTL

DRIVE = 8

| SLEW = FAST ;

```

# 3.11 Synthesize, Implement, and Generate Programmaing File

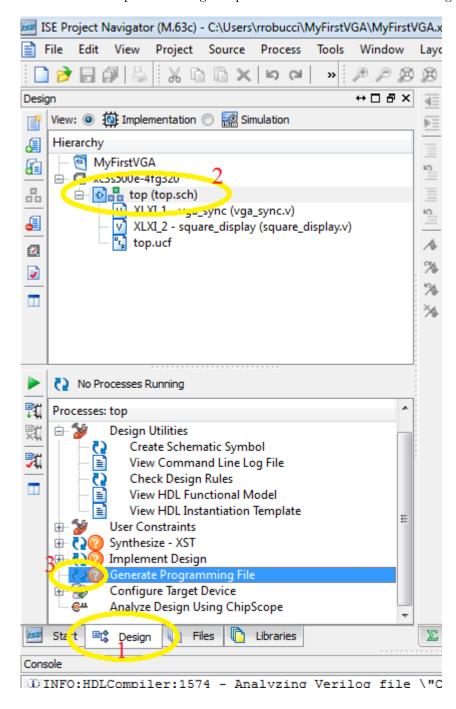

- 1. On the left, bring up the design view by clicking the design tab

- 2. Then in the Hierarchy plan, select the top module in the design, top.sch

- 3. Finally, DOUBLE-CLICK Generate Programming File in the plane below.

- "Synthesize" and "Implement Design" are run automatically as needed.

- Sythesize maps your design to a circuit based on FPGA build blocks.

- Implement Design maps the circuit to the FPGA including place and route.

#### 3.12 Program FPGA

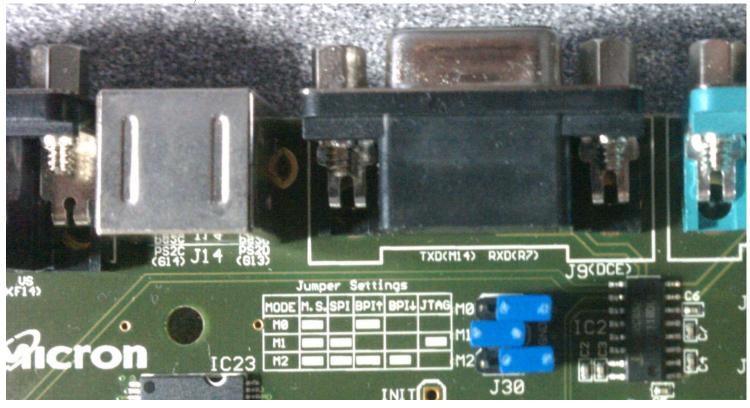

We will use the JTAG interface to program the FPGA. While normally separate separate from the FPGA board, the USB-to-JTAG interface is conveniently built into our starter board.

1. Set Jumper J30 to JTAG Setting

M0=open

M1 = short

M2 = open

DO NOT DISCARD JUMPERS, JUST PLACE THEM SO THEY ARE ATTACHED TO ONE PIN TO CREATE OPEN:

- 2. Connect USB Cable from board to computer

- 3. Plug in the board's power adaptor to the board's power connector and a  $120~\mathrm{V}$  outlet. Turn on the board using the power switch near the power connector.

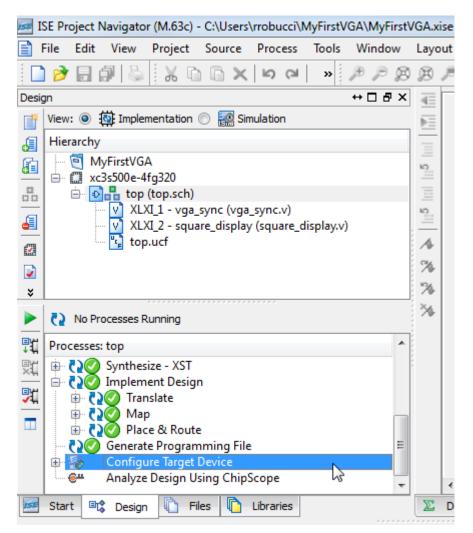

- 4. Double-Click "Configure Target Device" under "Generate Programing File"

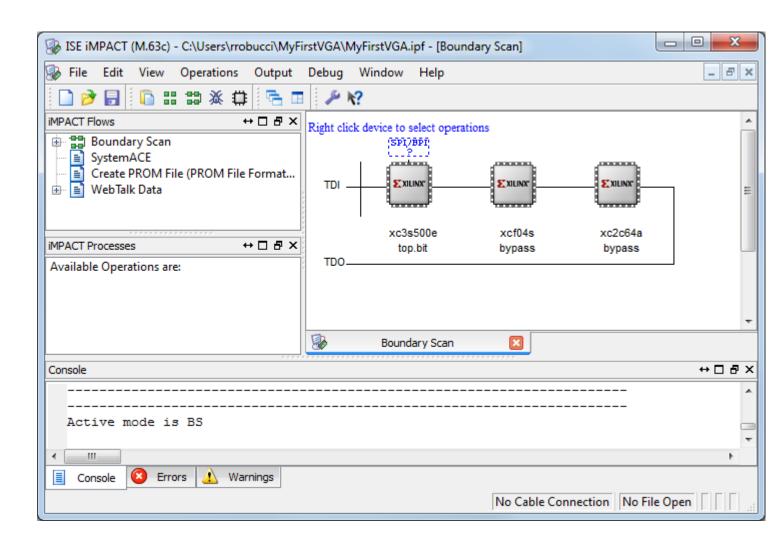

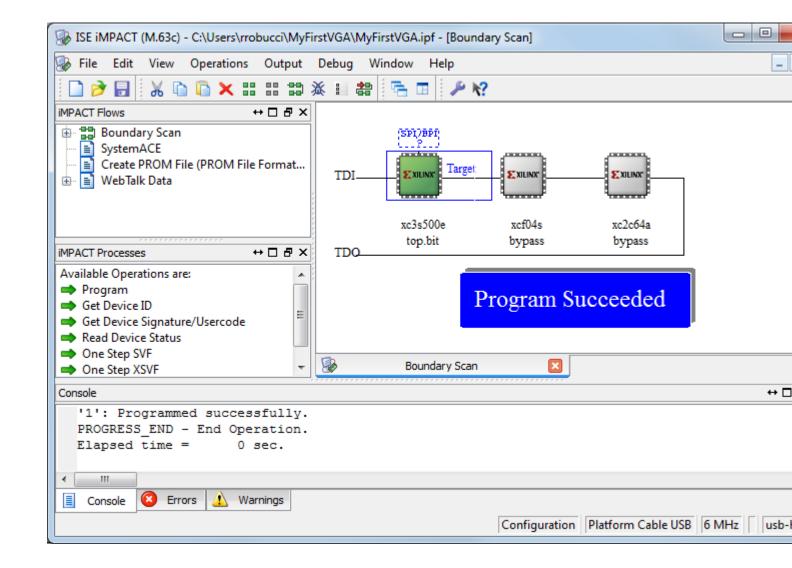

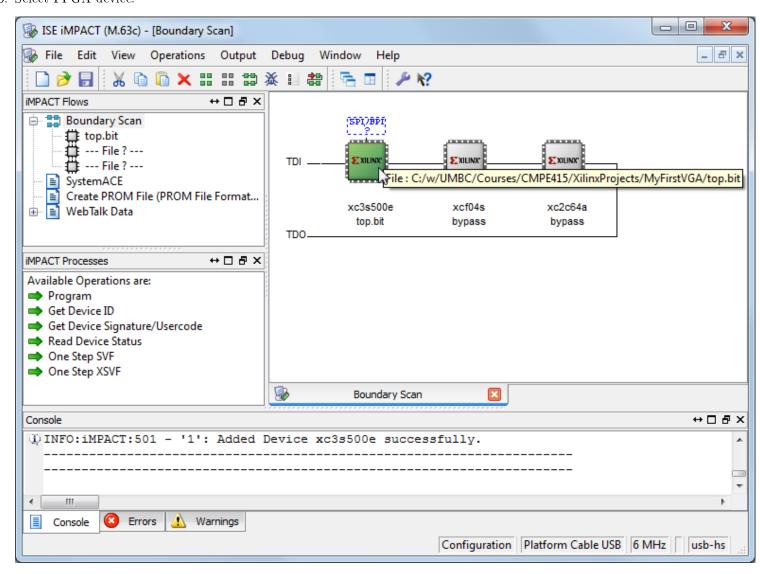

Result:

IF YOU DONT HAVE THIS RESULT SHOWING

THE DEVICE CHAIN THE FIRST TIME YOU

RUN THE TOOL, USE INTRUCTIONS IN SECTION 5 TO MANUALLY START iMPACT, PROGRAM YOUR DEVICE, AND SAVE YOUR CHAIN

CONFIGURATION (.ipf file)

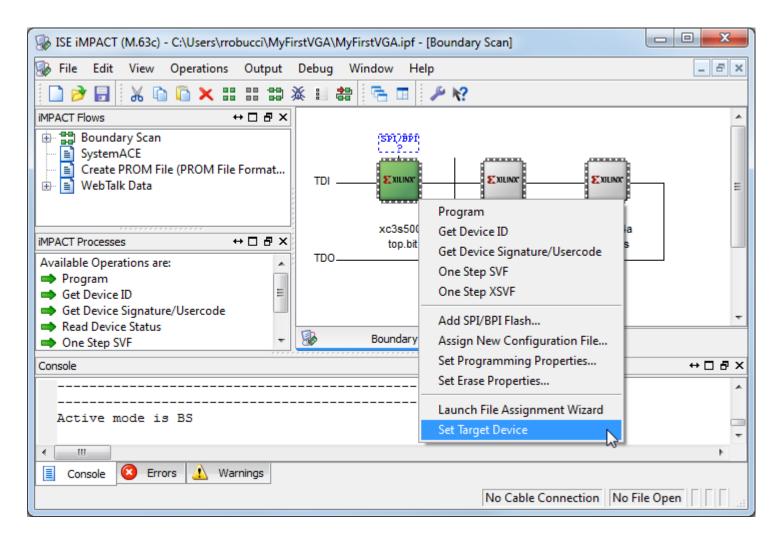

5. Right-click the xc3s500e device and select "Set Target Device"

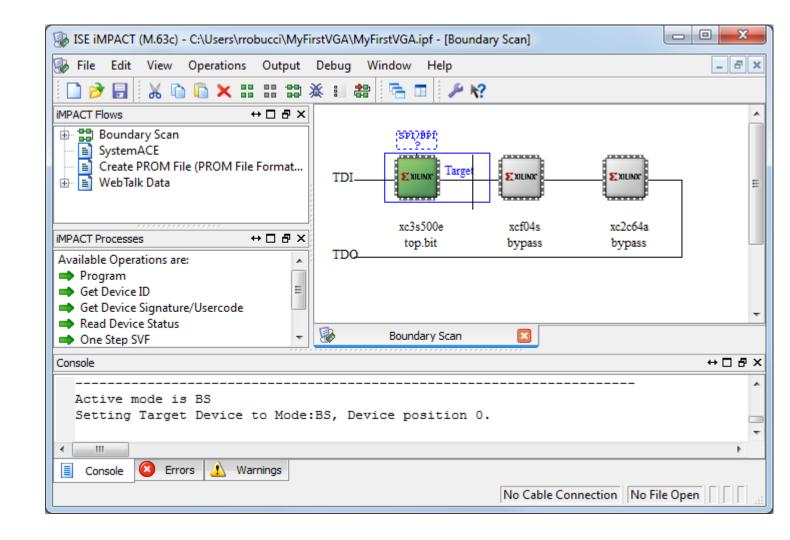

Result:

6. In iMACT, goto File->Save Project so that you aren't prompted to do this again when starting iMPACT.

Result:

#### 3.13 Connect to Monitor

Connect a VGA cable to the starter board and a monitor. You should see a magenta/purple rectange on a blue background.

# 4 Your Design Assignment:

Modify the design to have the ability to change the color of the rectangle and set the background to black based on switch positions.

- The color should be determined by turning on one of three switches, otherwise the rectangle is black.

- The three switches should correspond to yellow, cyan, and magenta. Having more than one switch on at a time is a "don"t care" condition.

The board's user manual provides a color chart in the VGA port section. It also provides and all the pin location information needed to add the appropriate information to your user contrainsts file for the switched.

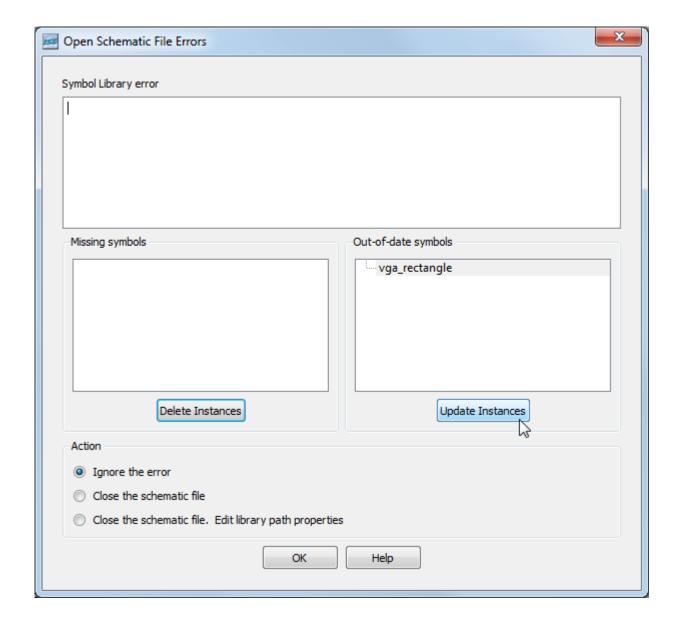

NOTE: When you update the port definitions of a module, you need to manually regenerate the symbol by running "Create Schematic Symbol" again. When you reopen a schematic with that symbol, it will present you with the option to update them. Just click "Update Intances".

# 5 Running iMACT Manually

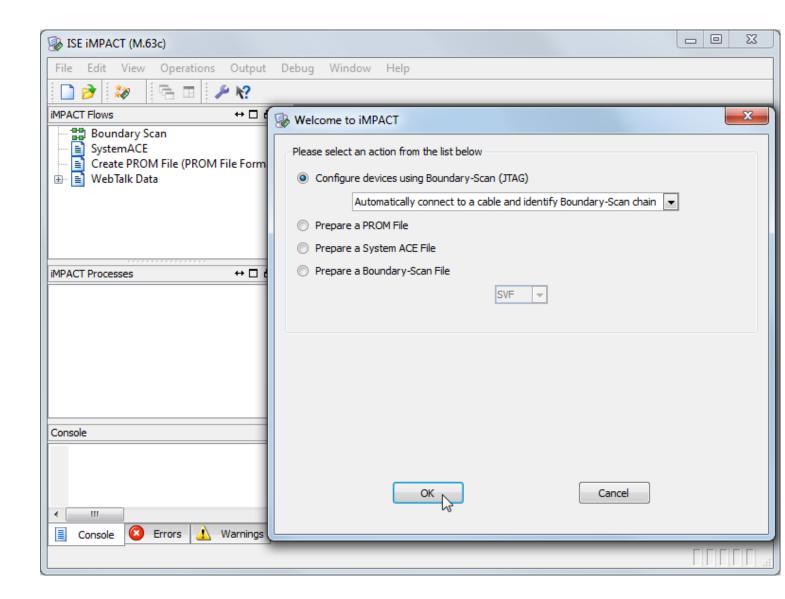

- 1. In ISE main menu: Tools->iMACT. Reply Yes/OK to any prompts.

- 2. In iMPACT menu, Edit->Launch Wizard...

- 3. Click OK

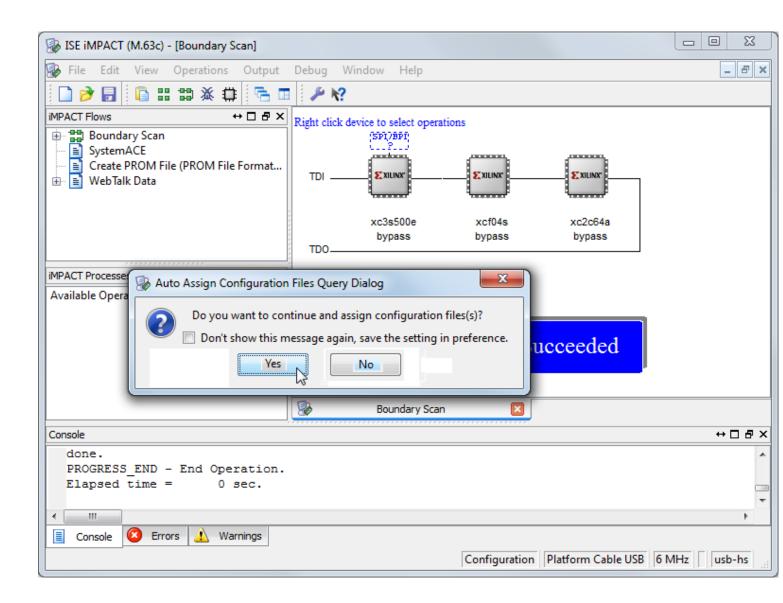

- 4. Click YES in following window.

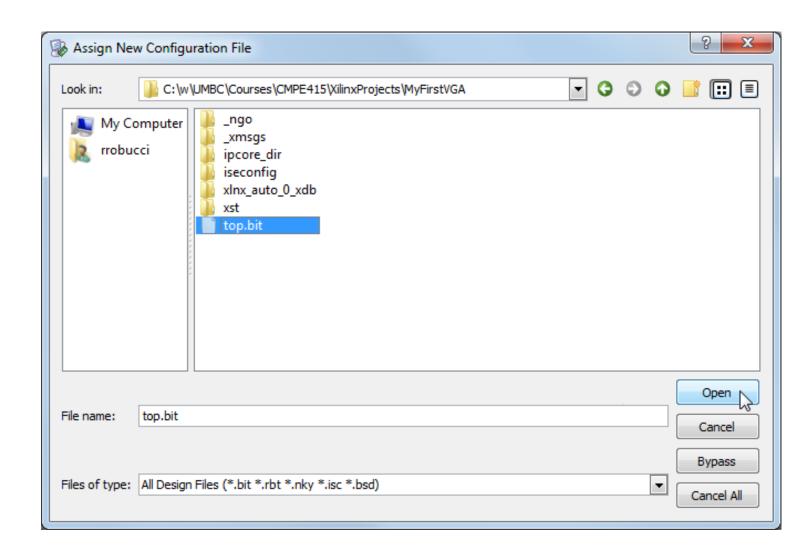

5. Select your bit file:

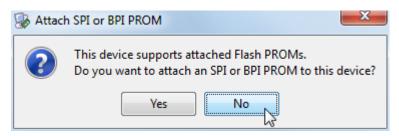

6. Select no (we will not load anything onto the FPGA ROM

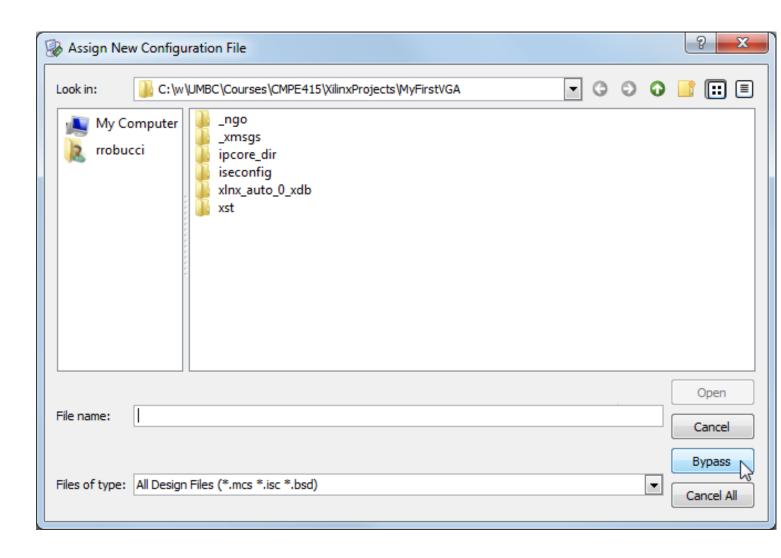

7. For the following two devices, select bypass:

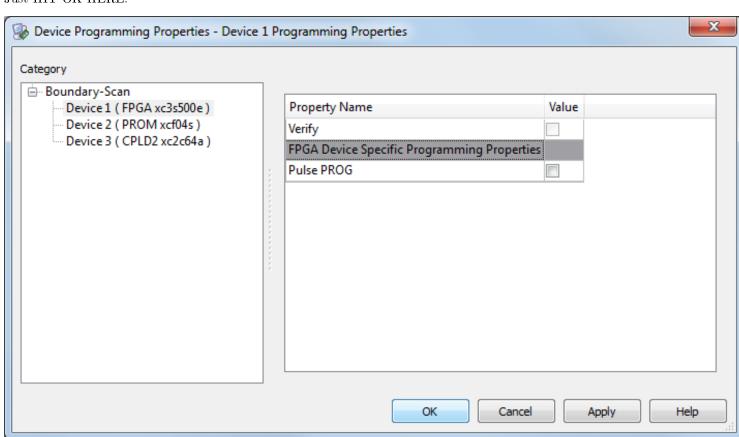

### 8. Just HIT OK HERE:

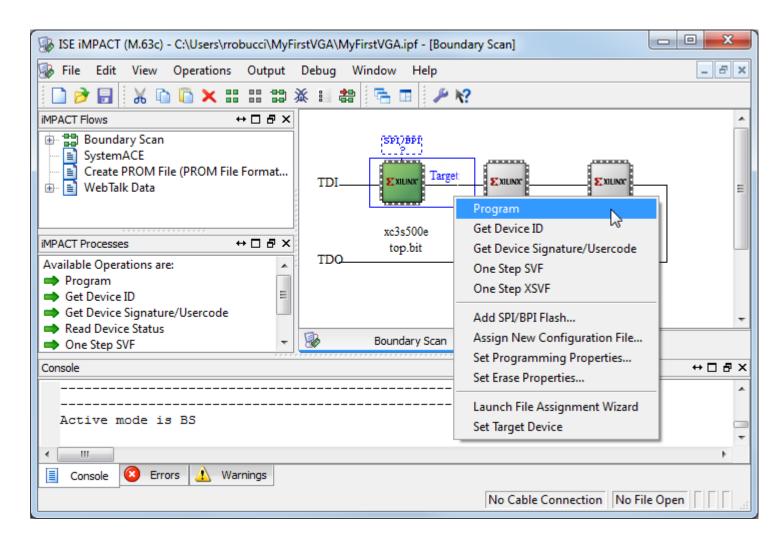

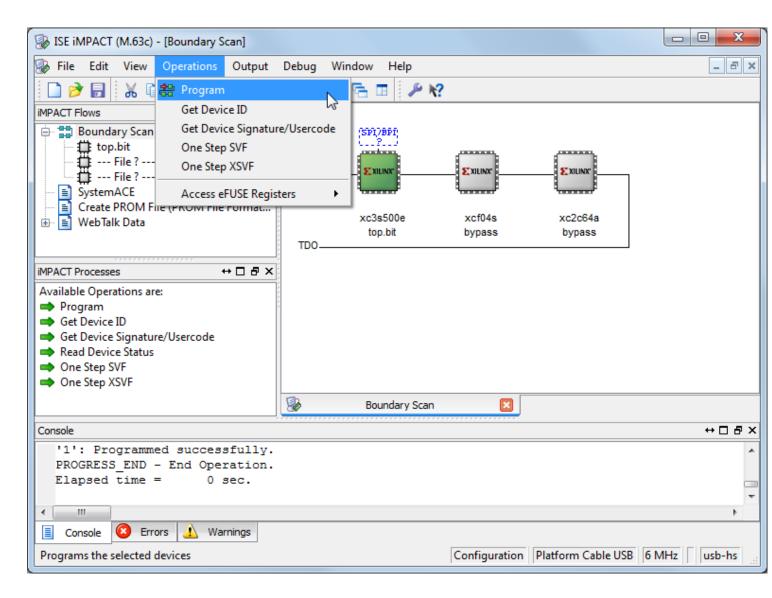

#### 9. Select FPGA device:

#### 10. Program device:

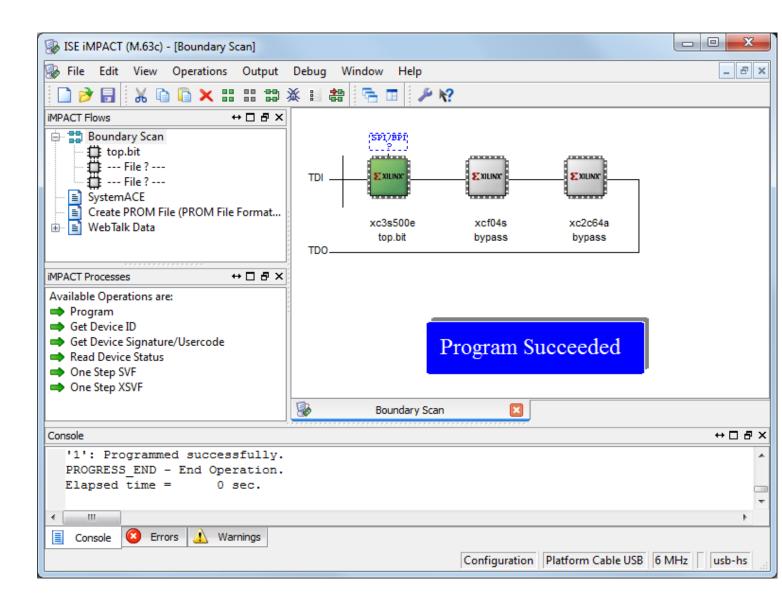

Result:

11. Use File -> Save Project to save chain configuration.

When you update your programming file (.bit) you may have to reload it by right-clicking the firt device in the chain, the FPGA, and using "Assign New Configuration File."