# CMSC 313 Lecture 21

- Last time: Karnaugh Map Examples

- Higher Dimension Karnaugh Maps

- Quine-McCluskey Algorithm

- Introduction to Sequential Logic

- Flip-Flops

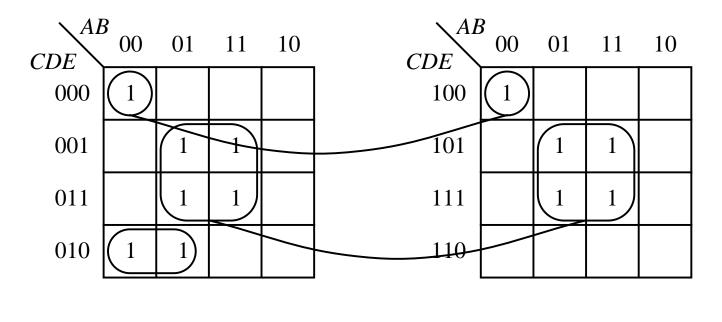

#### **Five-Variable K-Map**

Visualize two 4-variable K-maps stacked one on top of the other; groupings are made in three dimensional cubes.

$F = \overline{A} \,\overline{C} \,D \,\overline{E} \,+\, \overline{A} \,\overline{B} \,\overline{D} \,\overline{E} \,+\, B \,E$

**Appendix B: Reduction of Digital Logic**

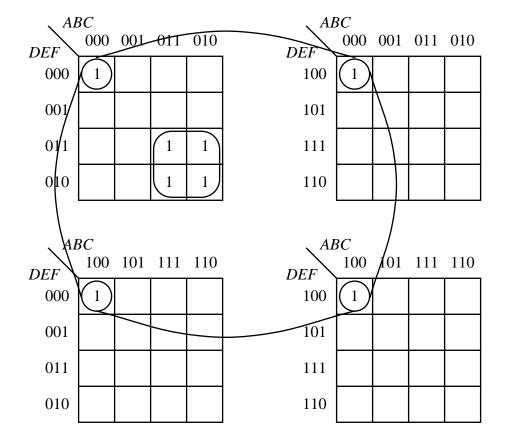

## **Six-Variable K-Map**

Visualize four 4-variable K-maps stacked one on top of the other; groupings are made in three dimensional cubes.

$G = \overline{B} \,\overline{C} \,\overline{E} \,\overline{F} + \overline{A} \,B \,\overline{D} \,E$

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

B-15

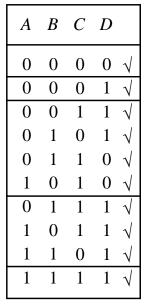

## **Truth Table with Don't Cares**

A truth table representation of a single function with don't cares.

| A | В | С | D | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | d |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | d |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | d |

Principles of Computer Architecture by M. Murdocca and V. Heuring

# **Tabular (Quine-McCluskey) Reduction**

- Tabular reduction begins by grouping minterms for which F is nonzero according to the number of 1's in each minterm. Don't cares are considered to be nonzero.

- The next step forms a consensus (the logical form of a cross product) between each pair of adjacent groups for all terms that differ in only one variable.

Initial setup

(a)

After first reduction

(b)

After second reduction

| A | В | С | D |   |

|---|---|---|---|---|

| 0 | _ | _ | 1 | * |

| _ | _ | 1 | 1 | * |

| _ | 1 | _ | 1 | * |

(c)

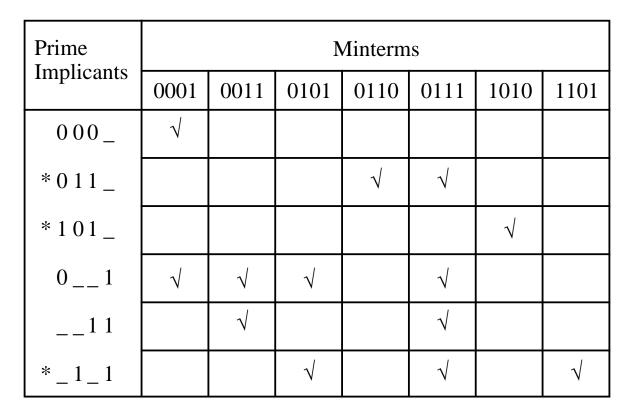

## **Table of Choice**

- The prime implicants form a set that completely covers the function, although not necessarily minimally.

- A table of choice is used to obtain a minimal cover set.

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

B-21

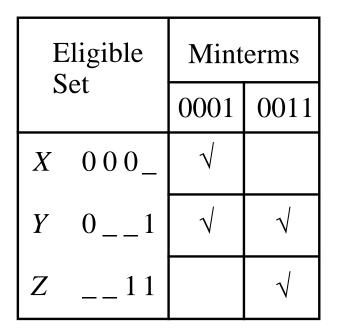

## **Reduced Table of Choice**

- In a reduced table of choice, the essential prime implicants and the minterms they cover are removed, producing the *eligible set*.

- $F = \overline{A}BC + A\overline{B}C + BD + \overline{A}D$

# **Multiple Output Truth Table**

• The power of tabular reduction comes into play for multiple functions, in which minterms can be shared among the functions.

| Minterm               | A | В | С | $F_0 F_1 F_2$ |

|-----------------------|---|---|---|---------------|

| $m_0$                 | 0 | 0 | 0 | 1 0 0         |

| $m_1$                 | 0 | 0 | 1 | 0 1 0         |

| $m_2$                 | 0 | 1 | 0 | 0 0 1         |

| <i>m</i> <sub>3</sub> | 0 | 1 | 1 | 1 1 1         |

| $m_4$                 | 1 | 0 | 0 | 0 1 0         |

| $m_5$                 | 1 | 0 | 1 | 0 0 0         |

| $m_6$                 | 1 | 1 | 0 | 0 1 1         |

| $m_7$                 | 1 | 1 | 1 | 1 1 1         |

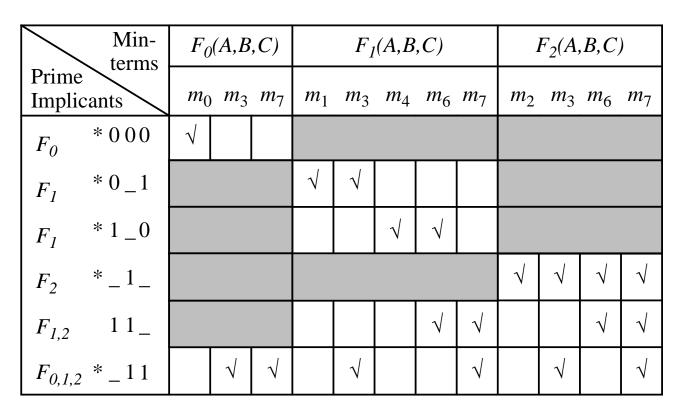

## **Multiple Output Table of Choice**

```

F_0(A,B,C) = \overline{A}\overline{B}\overline{C} + BC

F_1(A,B,C) = \overline{A}C + A\overline{C} + BC

F_2(A,B,C) = B

```

Principles of Computer Architecture by M. Murdocca and V. Heuring

# **Sequential Logic**

- The combinational logic circuits we have been studying so far have no memory. The outputs always follow the inputs.

- There is a need for circuits with memory, which behave differently depending upon their previous state.

- An example is a vending machine, which must remember how many and what kinds of coins have been inserted. The machine should behave according to not only the current coin inserted, but also upon how many and what kinds of coins have been inserted previously.

- These are referred to as *finite state machines*, because they can have at most a finite number of states.

Principles of Computer Architecture by M. Murdocca and V. Heuring

A-44

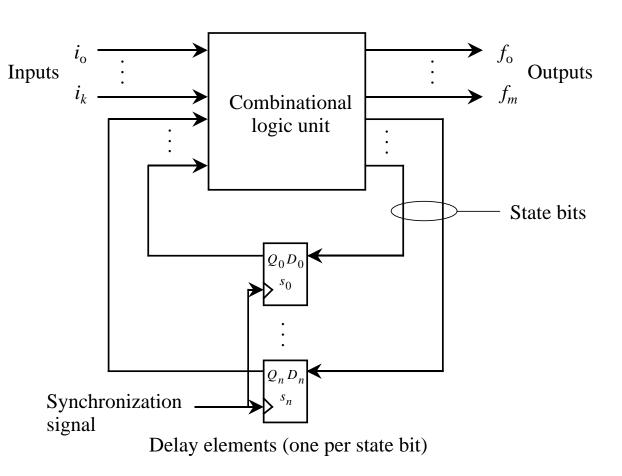

# Classical Model of a Finite State Machine

An FSM is composed of a composed of a combinational logic unit and delay elements (called *flip-flops*) in a feedback path, which maintains state information.

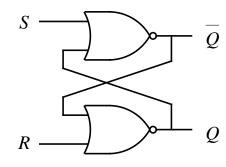

## S-R Flip-Flop

#### • The S-R flip-flop is an active high (positive logic) device.

| $Q_t$ | $S_t$ | $R_t$ | $Q_{i+1}$    |

|-------|-------|-------|--------------|

| 0     | 0     | 0     | 0            |

| 0     | 0     | 1     | 0            |

| 0     | 1     | 0     | 1            |

| 0     | 1     | 1     | (disallowed) |

| 1     | 0     | 0     | 1            |

| 1     | 0     | 1     | 0            |

| 1     | 1     | 0     | 1            |

| 1     | 1     | 1     | (disallowed) |

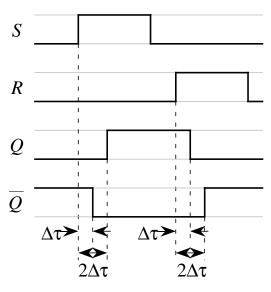

**Timing Behavior**

p-flop is an active high (po

Principles of Computer Architecture by M. Murdocca and V. Heuring

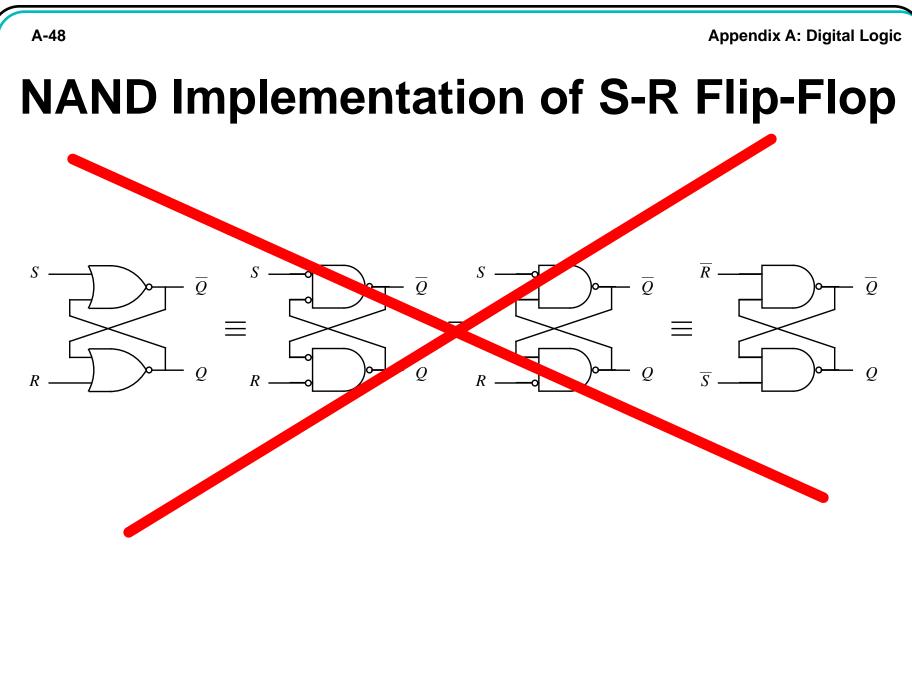

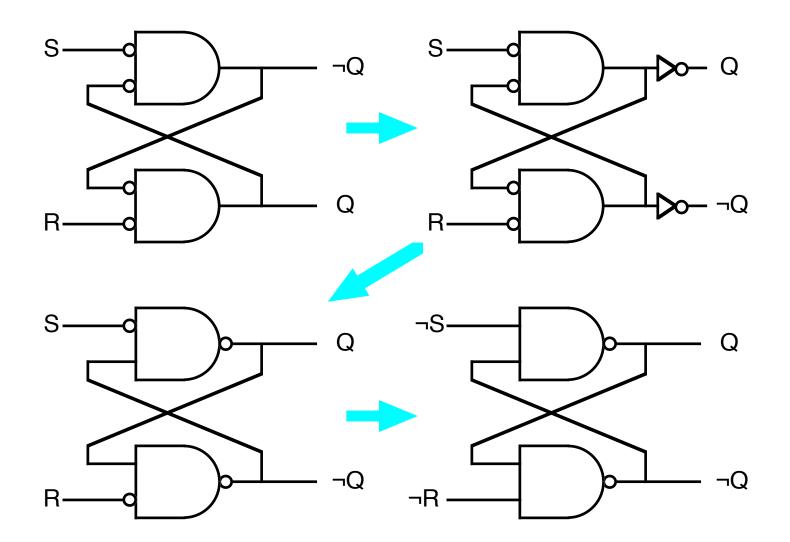

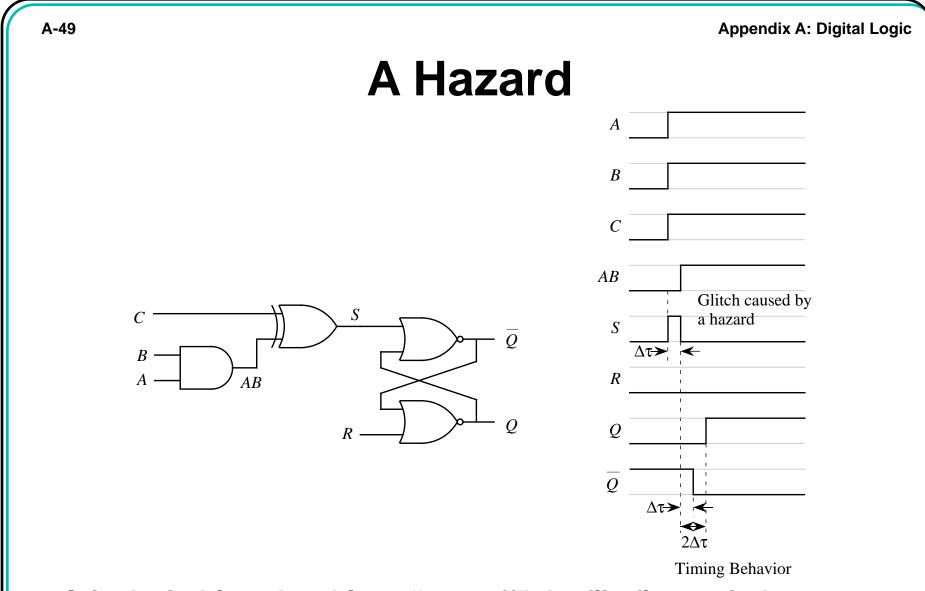

## SR Latch using NAND GATES

• It is desirable to be able to "turn off" the flip-flop so it does not respond to such hazards.

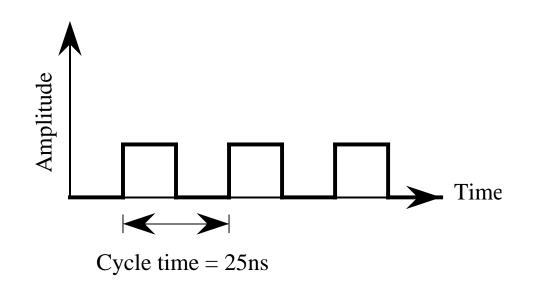

## A Clock Waveform: The Clock Paces the System

• In a positive logic system, the "action" happens when the clock is high, or positive. The low part of the clock cycle allows propagation between subcircuits, so their inputs settle at the correct value when the clock next goes high.

Principles of Computer Architecture by M. Murdocca and V. Heuring

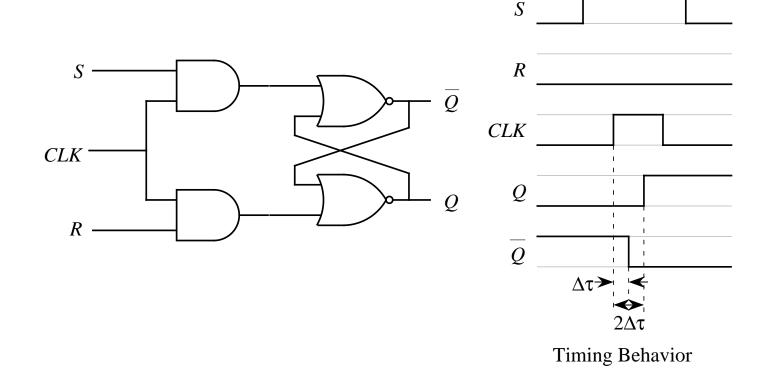

#### **Clocked S-R Flip-Flop**

#### • The clock signal, CLK, enables the S and R inputs to the flip-flop.

Principles of Computer Architecture by M. Murdocca and V. Heuring

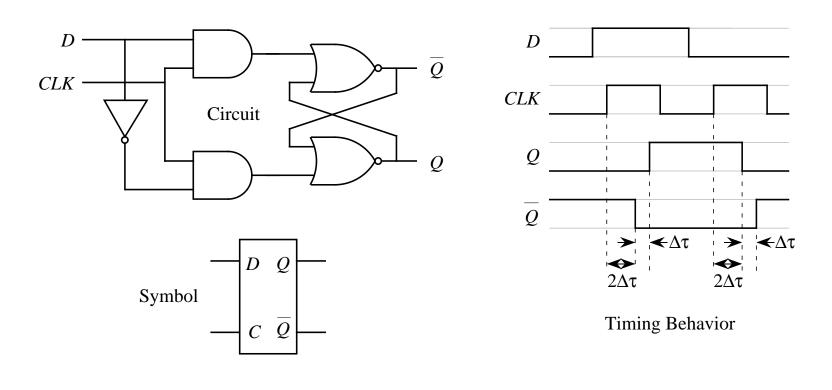

# **Clocked D Flip-Flop**

The clocked D flip-flop, sometimes called a *latch*, has a potential problem: If D changes while the clock is high, the output will also change. The *Master-Slave* flip-flop (next slide) addresses this problem.

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

A-53

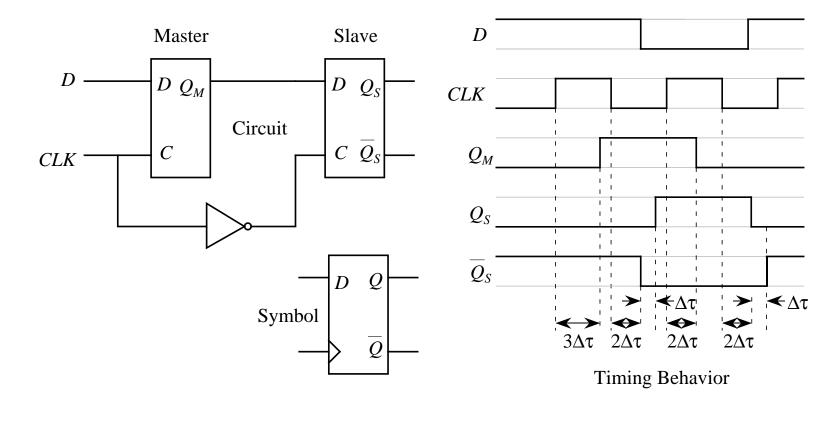

## **Master-Slave Flip-Flop**

• The rising edge of the clock loads new data into the master, while the slave continues to hold previous data. The falling edge of the clock loads the new master data into the slave.

© 1999 M. Murdocca and V. Heuring

A-54

## **Next Time**

- Edge-triggered Flip Flops

- Introduction to Finite State Machines